JESD204 IP

Filter

Compare

135

IP

from

25

vendors

(1

-

10)

-

JESD204 FPGA IP

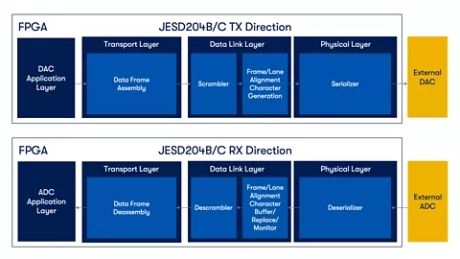

- The JEDEC committee created the JESD204 data converter serial interface standard to standardize and reduce the number of data inputs/outputs between high-speed data converters and other devices, such as FPGAs

- The protocol has many advantages, such as simplified layouts, skew management, and deterministic latency.

-

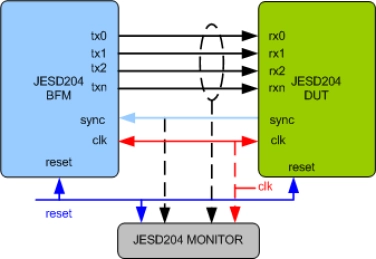

JESD204 Verification IP

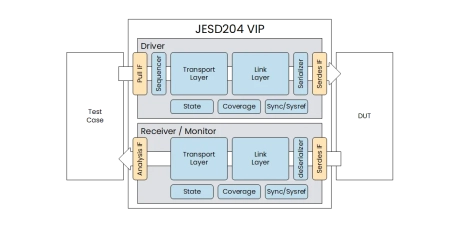

- This JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging these standards in a UVM simulation environment.

- The verification IP helps reduce time to test, accelerate verification process and ensures a high quality for the end-product.

-

Simulation VIP for JESD204

- Topology

- Transmitter or receiver configuration

- Clock Frequency

- Any frequency is supported, as the VIP works on the source clock

-

JESD204 Verification IP

- Follows JESD204 specification JESD204A, JESD204B, JESD204C and JESD204D.

- Supports Transmitter and Receiver Mode.

- Supports data interfaces up to 116 Gbps with PAM4 and up to 58 Gbps with PAM2 in PHY layer.

- Supports up to 32 lanes.

-

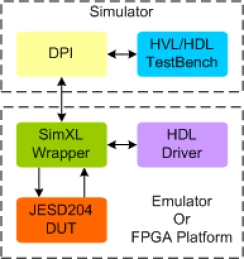

JESD204 Synthesizable Transactor

- Follows JESD204 specification JESD204A, JESD204B and JESD204C

- Supports Transmitter and Receiver Mode

- Supports up to 32 lanes

- Supports 32bit data width per converter

-

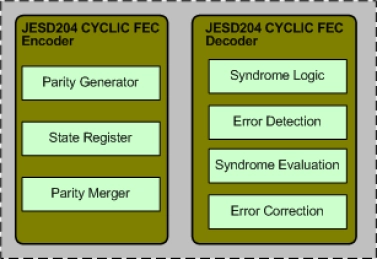

JESD204 CYCLIC FEC IIP

- Compliant with JESD204 specification JESD204C.

- Supports Full JESD204C FEC functionality.

- This FEC(Forward Error correction) methodology implements the (2074, 2048) binary cyclic code is shortened from the cyclic Fire code (8687, 8661).

- Supports FEC of 26 bits parity bits.

-

JESD204 PHY

- Designed to JEDEC® JESD204B

- Supports 1 t0 12 lane configurations

- Supports Subclass 0, 1, and 2

- Physical layer functions provided

-

JESD204

- Designed to JEDEC JESD204B specification

- Supports scrambling and initial lane alignment

- Supports 1-256 Octets per frame and 1-32 frames per multi-frame

- Supports 1 to 32 lane configurations

-

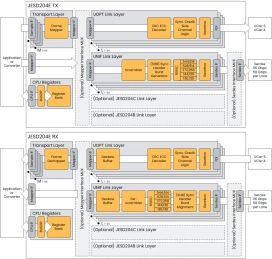

JESD204E Controller IP

- The JESD204E Controller IP from Chip Interfaces is an early adopter’s version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters.

- The JESD204-E IP core supports the UCIe Optimized Link Layer, a dedicated mode to run JESD over UCIe Modules with Line rates up the 64Gbps per bump, and a JESD204D backwards compatible mode called the Unified Link Layer with line speeds up to 116Gbps with PAM4 and 58Gbps with NRZ and full FEC support.

-

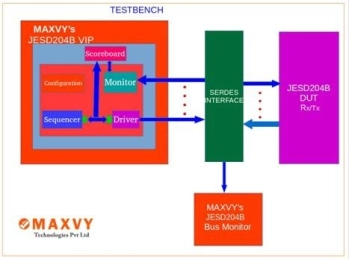

JESD204B UVM VIP

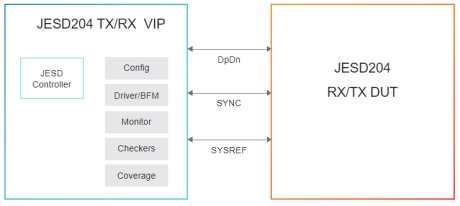

- The vendor provides configurable JESD204B TX/RX verification IP

- JESD204B is a Serial Interface for Data Converters which are defined by JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

- Our VIP covers Transport and Data link layer functionality of JESD204B

- The VIP provides more flexible configuration to user to select their needs like lane,device configuration, data width