Image Recognition IP

Filter

Compare

10

IP

from

8

vendors

(1

-

10)

-

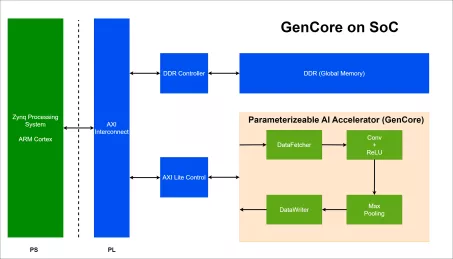

AI Accelerator Specifically for CNN

- A specialized hardware with controlled throughput and hardware cost/resources, utilizing parameterizeable layers, configurable weights, and precision settings to support fixed-point operations.

- This hardware aim to accelerate inference operations, particulary for CNNs such as LeNet-5, VGG-16, VGG-19, AlexNet, ResNet-50, etc.

-

Visibility Improver IP

- Improves the visibility in various shooting conditions.

- Supports both AXI4-stream I/F and DE (data enable) I/F as input/output video interface.

- Selectable starting by software or hardware event.

-

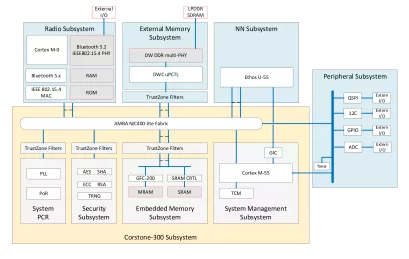

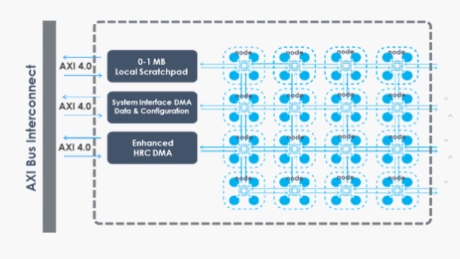

IP platform for intelligence gathering chips at the Edge

- High performance IoT solutions for AI at the Edge can now be created up to 30% faster

-

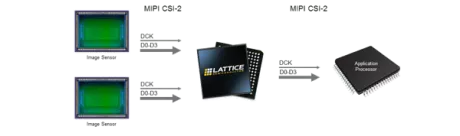

Two Input to One Output MIPI CSI-2 Camera Aggregator Bridge

- Supports MIPI CSI-2 inputs and outputs at up to 6 Gbps

- Combines two MIPI CSI-2 inputs to one MIPI CSI-2 output

- Supports all CSI-2 data types

- Compliance with MIPI D-PHY Specification v1.1

-

Four Input to One Output MIPI CSI-2 Camera Aggregator Bridge

- Supports MIPI CSI-2 inputs and outputs at up to 6 Gbps: 1, 2 or 4 Data Lanes

- Merges two of four MIPI CSI-2 inputs to one MIPI CSI-2 output

- Supports all CSI-2 data type: RAW, RGB, YUV

- Compliance with MIPI D-PHY Specification v1.1

-

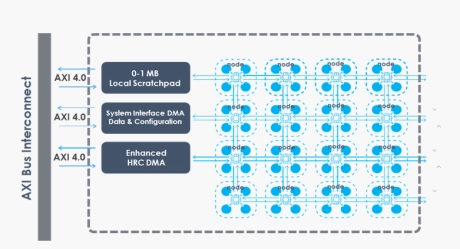

Neuromorphic Processor IP (Second Generation)

- Supports 8-, 4-, and 1-bit weights and activations

- Programmable Activation Functions

- Skip Connections

- Support for Spatio-Temporal and Temporal Event-Based Neural Network

-

Neuromorphic Processor IP

- Supports 4-, 2-, and 1-bit weights and activations

- Supports multiple layers simultaneously

- Convolutional Neural Processor (CNP) and

- Fully-connected Neural Processor (FNP)

-

Safety Enhanced GPNPU Processor IP

- A True SDV Solution

- Fully programmable – ideal for long product life cycles

- Scalable multicore solutions up to 864 TOPS

- Solutions for ADAS, IVI and ECU products

-

Color Camera Sensor Bayer Decoder

- Converts Bayer image into the RGB image

- Supports all Bayer pattern combinations

- Optional built-in LVDS receiver compatible with the Micron MT9V022 automotive sensor

- Unlimited vertical pixel resolution