I3C Device IP

Filter

Compare

105

IP

from

24

vendors

(1

-

10)

-

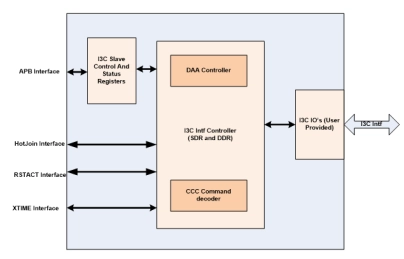

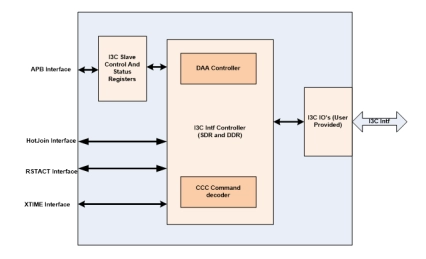

I3C Device Controller IP v1.2

- The I3C Device Controller IP Implements Device Controller functionality as defined by the MIPI Alliance’s I3C Specification.

- The I3C bus is used for various sensors in the mobile/automotive system where an I3C Host Controller transfers data and control information between itself and various sensor devices.

-

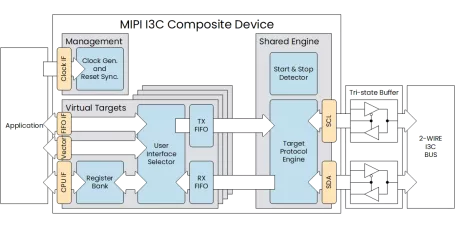

MIPI I3C Target Device

- MIPI I3C Basic Specification v1.2 compiliance

- Native 32-bit CPU Interface

- Optional CPU interface wrappers (APB, AHB, AXI)

- Legacy I2C communication with 7-bit Static Address

- I3C Single Data Rate (SDR) mode

-

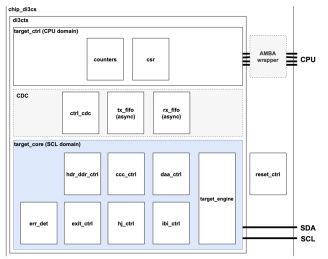

I3C 1.1 Device Controller

- The I3C Device Controller IP Implements Device Controller functionality as defined by the MIPI Alliance’s I3C Specification.

- The I3C bus is used for various sensors in the mobile/automotive system where an I3C Host Controller transfers data and control information between itself and various sensor devices.

- The I3C Device Controller IP can be easily integrated into the Sensor/Device Controllers with minimal gate count.

-

-

TSMC N4P 1.2V/1.8V I3C MS Add-on

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection

-

TSMC N4P 1.2V/1.8V I3C

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection

-

TSMC N7 1.8V/3.3V I3C with CDM 7A, AG2 Platform

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection

-

TSMC N6 1.8V/2.5V/3.3V I3C IO

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection

-

TSMC N5A 1.2V/1.8V I3C AG2 Platform Metal Add-on

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection

-

TSMC N5A 1.2V/1.8V I3C AG2 Platform

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection