HyperBus controller IP

Filter

Compare

7

IP

from

5

vendors

(1

-

7)

-

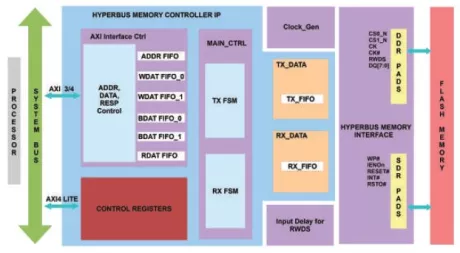

Hyperbus Flash Memory Controller

- Compatible with spansion hyperbus based memory products.

- 0 Wait State Write Burst Operation for HyperBus memory on AXI interface of up to 256 words.

-

HYPERBUS™ Memory Controller

- The HyperBus™ Memory Controller IP Core is a high-speed, fully configurable SPI master/slave solution, designed for seamless integration into modern SoC and FPGA architectures.

- Building on the proven DFSPI core, this IP bridges easily to APB, AHB, and AXI buses, supporting SINGLE, DUAL, QUAD, and OCTAL SPI modes for maximum design flexibility.

-

xSPI Multiple Bus Memory Controller

- SLL’s unified xSPI Multiple Bus Memory Controller IP supports the widest range of JEDEC xSPI and xSPI-like NOR Flash and PSRAM memories (JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0, 2.0 and 3.0, OctaBus and Xccela Bus) that are available now from many memory vendors.

- JEDEC xSPI and xSPI-like memories offer good performance with lower hardware and power costs. Memory device variants offer up to 512 Mbit PSRAM, up to 2 Gigabit NOR Flash, up to 250 MHz DDR clock speeds, with x4, x8 and x16 data path widths, and a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints. Some PRSAM devices are now also available with internal ECC.

-

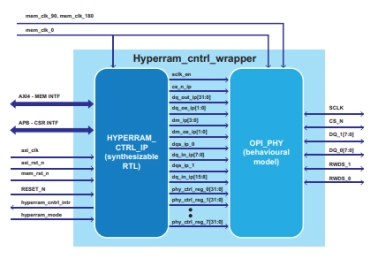

Winbond HyperRAM Controller

- The HyperRAM controller supports Winbond’s HyperBus based HyperRAM devices

- This controller enables smooth integration of Winbond’s HyperBus HyperRAM memory chips into various new-gen SoCs’.

-

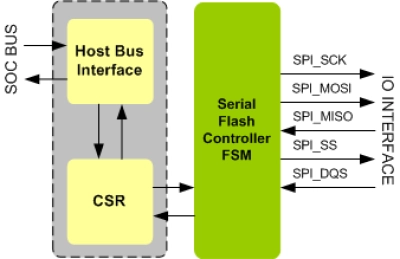

Serial Flash Controller IIP

- Compliant with Flash Devices from major Flash Device Vendors.

- Full Flash with SPI Master Functionality.

- Supports 3 modes of operation

- Slave Mode - Accessing flash device through CSR registers from SOC Slave interface

-

-

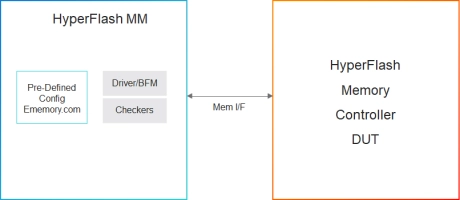

Simulation VIP for HyperFlash

- Density

- From 128Mb to 512Mb

- General Functionality

- Supports Status Register Read and Clear commands