GF14nm DDR4/LPDDR PHY Controller IP

Filter

Compare

5

IP

from

3

vendors

(1

-

5)

-

DDR4/LPDDR4 PHY Interface

- The DDR PHY IP is a combination of hard macro, I/O Pad and synthesizable RTL to provide a physical interface to JEDEC standard DDR3/DDR4 SDRAM memories.

- The synthesizable RTL (ddr_phy_top) provides control functions such as initialization, SDRAM interface training, impedance calibration and programmable configuration controls.

-

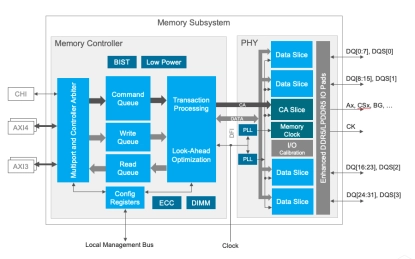

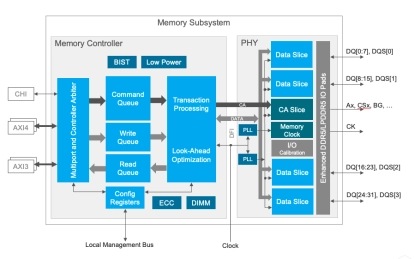

DDR/LPDDR Controller

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 and DDR5/4/3 protocol memories

- Memory controller interface complies with DFI standards up to version 5.0

- Priority per command on Arm® AMBA® 4 AXI, AMBA 3 AXI

-

DDR/LPDDR PHY

- DDR5/4/3 training with write-leveling and data-eye training

- Optional clock gating available for low-power control

- Internal and external datapath loop-back modes

- I/O pads with impedance calibration logic and data retention capability

- Programmable per-bit (PVT compensated) deskew on read and write datapaths

- RX and TX equalization for heavily loaded systems

-

DDR4/LPDDR4 Controller

- On the host side, DDR4/LPDDR4 Controller supports up to 16 AMBA4 AXI. The configuration registers are programmed through the APB interface.

- On the DFI side, DDR4/LPDDR4 Controller supports for intergration with DFI4.0-compliant PHY.

-

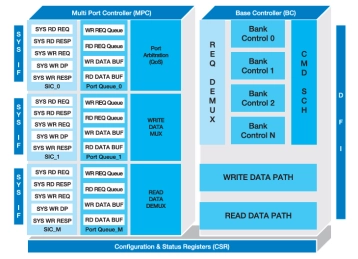

Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC Controller is a highly flexible and configurable design. It is targeted for high bandwidth access and low power consumption such as next generation mobile, DDR/LPDDR networking and consumer applications.

- The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.