GDDR6 on Samsung 14LPP IP

Filter

Compare

13

IP

from

6

vendors

(1

-

10)

-

GDDR6 PHY IP on GF 12nm LPP

- The UniIC GDDR6 PHY,subsequently referred to as the UNIIC_GD6PHY, is designed for performance and power efficiency, its target is to deliver industry-leading data rates of up to 12Gbps/13Gbps/14Gbps and is compatible with JEDEC standard JEDEC250 and DFI 3.1

- The UNIIC_GD6PHY is used to transfer the Command/Address and Datas between the memory controller and the GDDR6 DRAM device; _x000D_ The UNIIC_GD6PHY is available in Global Foundries FinFET 12LPP technology

- The UNIIC_GD6PHY is fully documented and comes with a comprehensive set of deliverables for ease of system modeling and integration.

-

Simulation VIP for GDDR6

- Speed

- Supports up to 16Gbps with current vendor datasheets

- Device Density

- Supports a wide range of device densities from 8Gb to 32Gb

-

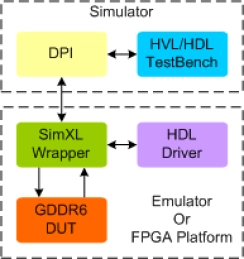

GDDR6 Synthesizable Transactor

- Supports 100% of GDDR6 protocol standard JESD250, JESD250A, JESD250B and JESD250C specification with version 3.12

- Supports all the GDDR6 commands as per the specs

- Supports 2 separate independent channels with point-to-point interface for data, address and command

- Supports double data rate (DDR) or quad data rate (QDR) data

-

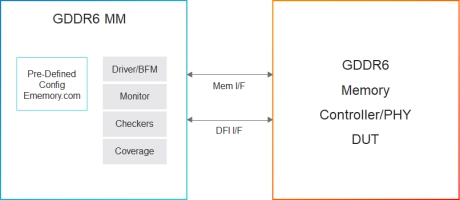

GDDR6 Memory Model

- Supports GDDR6 memory devices from all leading vendors.

- Supports 100% of GDDR6 protocol standard JESD250, JESD250A, JESD250B and JESD250C specification with version 3.12.

- Supports all the GDDR6 commands as per the specs.

- Supports 2 separate independent channels with point-to-point interface for data, address and command.

-

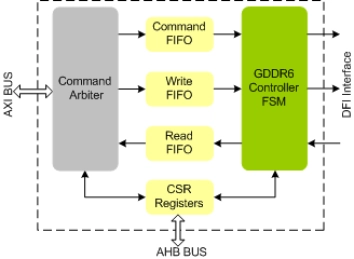

GDDR6 Controller IIP

- Supports GDDR6 protocol standard JESD250, JESD250A and JESD250B specification with version 3.11.

- Compliant with DFI-version 4.0 or 5.0 Specification.

- Supports all the GDDR6 commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

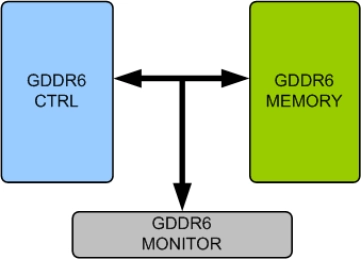

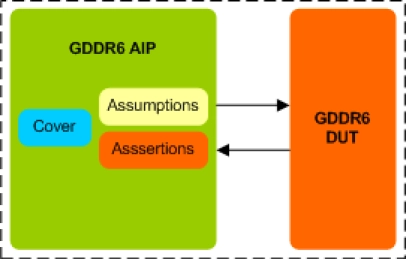

GDDR6 Assertion IP

- Specification Compliance

- Compliant to ARM GDDR6 protocol

- Supports GDDR6 memory devices from all leading vendors.

- Supports 100% of GDDR6 protocol standard JESD250, JESD250A, JESD250B and JESD250C specification with version 3.12.

-

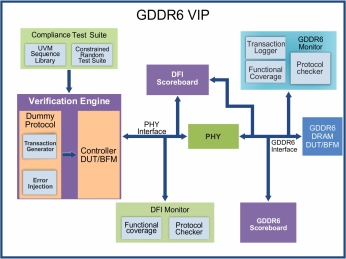

GDDR6 Verification IP

- Compliant to JEDEC GDDR6 SDRAM Specification version JESD250B.

- Supports connection to any GDDR6 Memory Controller IP communicating with a JESD250B compliant GDDR6 Memory Model.

- Supports configurable SDRAM addressing of different sizes (x8 and x16).

- Available in all memory sizes from 4 Gb to 16 Gb per channel.

-

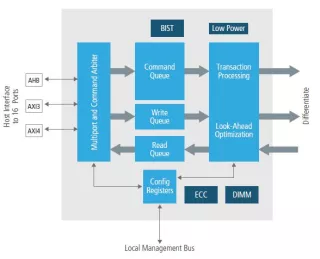

GDDR6 Controller

- In-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compatible with GDDR6 devices compliant to JESD250b

- Single and multi-port host options for Arm® AMBA®4, AMBA 3 AXI, and low-latency Denali interfaces

- QoS features allow command prioritization

- Flexible paging policy

-

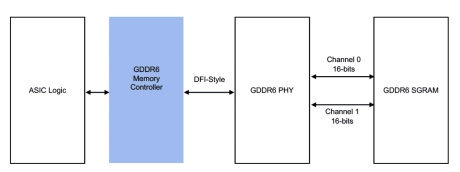

GDDR6 Controller

- Supports up to 24 Gb/s per pin operation

- Can handle two x16 GDDR6 channels with one controller or independently with two controllers

- Supports x8 or x16 clamshell mode

- Queue-based interface optimizes performance and throughput

- Maximizes memory bandwidth and minimizes latency via Look-Ahead command processing

- Automatic retry on transactions where EDC error detected

-

LPDDR Controller

- Memory controller interface complies with DFI standard up to 5.0

- Application-optimized configurations for fast time to delivery and lower risk

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 protocol memories

- Priority per command on Arm®AMBA® 4 AXI, AMBA 3 AXI