Extreme Ethernet IP

Filter

Compare

9

IP

from

3

vendors

(1

-

9)

-

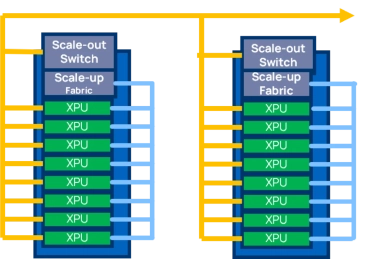

Scalable Switch Fabric

- The NeuraScale Scalable Switch Fabric is a WeaveIP™ advanced system IP solution that is designed from the ground-up to provide non-blocking switching between a large number of UALink™, Ultra Ethernet, or AMBA ports for the emerging scale-up and scale-out systems.

- Extreme port density is achieved while maintaining near lowest theoretical latency, tight latency-bandwidth curve and simple physical design with design tiles.

-

1-56Gbps Serdes - 7nm (Multi-reference Clock)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Ultra Low Latency)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Area-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-112Gbps Serdes - 7nm

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (PPA-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

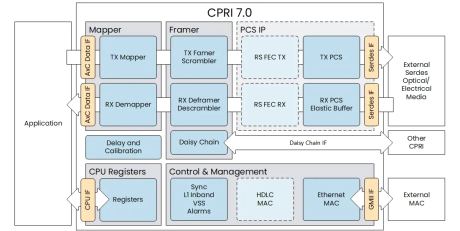

CPRI 7.0

- The Common Public Radio Interface (CPRI) 7.0 core is a silicon agnostic implementation of the CPRI 7.0 specification, which is targeting both ASIC and FPGAs CPRI.

- CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems.

- With its extreme flexibility and reduced logic consumption, the CPRI 7.0 IP core is the perfect match whether the application is REC (Radio Equipment Controller) or RE (Radio Equipment).

-

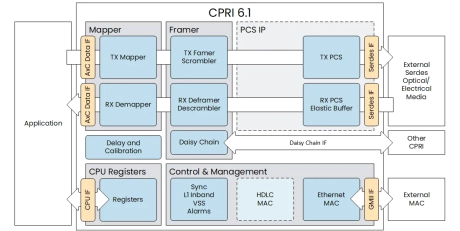

CPRI 6.1

- Common Public Radio Interface (CPRI) 6.1 core is a silicon agnostic implementation of the CPRI 6.1 specification, which is targeting both ASIC and FPGAs.

- CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems.

-

1-56Gbps Serdes - 16/12nm

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.