Dual Port Register File IP

Filter

Compare

15

IP

from

7

vendors

(1

-

10)

-

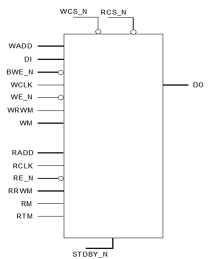

Dual Port Register File Compiler (1 Read-only port, 1 Write-only port) - GF 22FDX+

- Uses 8T-TP185SL bit cells.

- Isolated Supplies: Periphery and array power domains can be independently powered down in standby mode.

- Deep Sleep Standby Mode: Memory retains data at minimal power via internal biasing.

-

Dual Port (1 read only port, 1 write only port) Register File Compiler on N22ULL

- Ultra-Low Leakage: High VT (HVT) are used to minimize leakage performance.

- Bit Cell: Utilizes Foundries 8T bit cells to ensure high manufacturing yields

- Deep Sleep Mode Retains data a minimal power consumption.

-

Single Port Register File compiler - Memory optimized for high density and high speed - Dual voltage - compiler range up to 40 k

- Configuration

- SVT transistors for memory periphery

- uHD HVT pushed rule bit-cell from foundry

- High speed

-

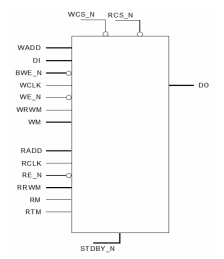

Two Port Register File compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 64 k

- 1. Reduce the die cost

- Unique architecture optimizing the periphery area for outstanding area gain

- 2. Extend the battery life

- Leakage reduction thanks to careful design structures,optional retention mode and choice of SVT/HVT periphery

-

Single Port Register File compiler - Memory optimized for high density and speed - Dual Voltage - Compiler range up to 40 kbits

- Decrease of fabrication costs

- Up to 50% denser than traditional register file compilers!

- Ultra low dynamic power

- Low power architecture even at nominal voltage: Up to 50% less consuming than standard memory compilers available at 90 nm LP

-

Single Port Register File compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 40 k

- FOUNDRY SPONSORED

- HIGHEST DENSITY

- -Smart periphery design for significant gain in density

- EXTENDED BATTERY LIFE

-

Two Port Register File compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 64 k

- 1. Reduce the die cost

- Unique architecture optimizing the periphery area for outstanding area gain

- 2. Extend the battery life

- Leakage reduction thanks to careful design structures,optional retention mode and choice of SVT/HVT periphery

-

Single Port Register File compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 40 k

- REACH HIGHEST DENSITY

- Smart periphery design for significant gain in density

- EXTEND BATTERY LIFE

- Data retention mode at 1.2 V and 0.9 V to divide drastically the leakage compared to simple stand by mode