DisplayPort link controller IP

Filter

Compare

48

IP

from

8

vendors

(1

-

10)

-

DisplayPort Link Policy Maker

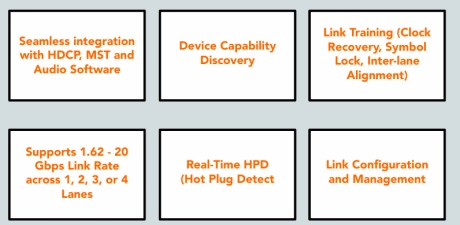

- The DisplayPort Link Policy Maker (LPM) is a DisplayPort 1.4/2.0 compliant software stack that manages and controls the DisplayPort serial link and AUX channel communications.

- The software provides for enumeration and configuration of the source and sink devices, adaptive training of the DisplayPort link, video stream allocation and transmission, AUX channel traffic management and handling of all HPD (Hot Plug Detect) events.

-

DisplayPort Transmit Controller ASIL Compliant

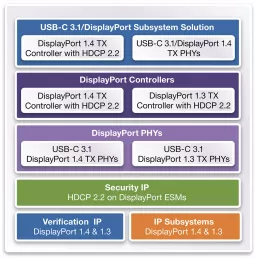

- Industry’s only USB Type-C IP solution consisting of USB-C 3.1/DisplayPort 1.3 Tx PHYs, USB-C 3.1/DisplayPort 1.3 Tx controllers with HDCP 2.2 and HDCP 1.4 content protection, verification IP, IP subsystems, IP prototyping kits, and IP software development kits

- Solution supports USB Type-C, SuperSpeed USB 3.1 at 10 Gbps, SuperSpeed USB 3.0 at 5 Gbps and High-Speed USB (USB 2.0) as well as DisplayPort 1.3 Tx supporting RBR, HBR1, HBR2 and HBR3 bitrates

- Controllers support Device, Host, and Dual-Role Device USB-C 3.1 as well as DisplayPort 1.3 Tx with HDCP 2.2 content protection

-

DisplayPort Transmit Controller

- Industry’s only USB Type-C IP solution consisting of USB-C 3.1/DisplayPort 1.3 Tx PHYs, USB-C 3.1/DisplayPort 1.3 Tx controllers with HDCP 2.2 and HDCP 1.4 content protection, verification IP, IP subsystems, IP prototyping kits, and IP software development kits

- Solution supports USB Type-C, SuperSpeed USB 3.1 at 10 Gbps, SuperSpeed USB 3.0 at 5 Gbps and High-Speed USB (USB 2.0) as well as DisplayPort 1.3 Tx supporting RBR, HBR1, HBR2 and HBR3 bitrates

- Controllers support Device, Host, and Dual-Role Device USB-C 3.1 as well as DisplayPort 1.3 Tx with HDCP 2.2 content protection

-

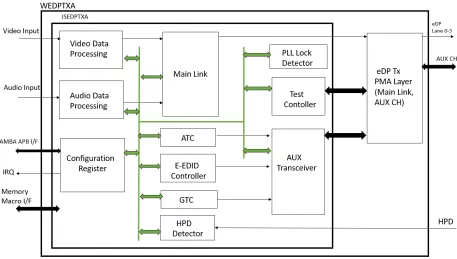

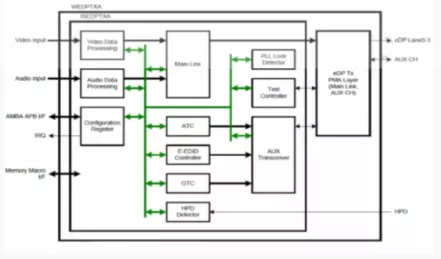

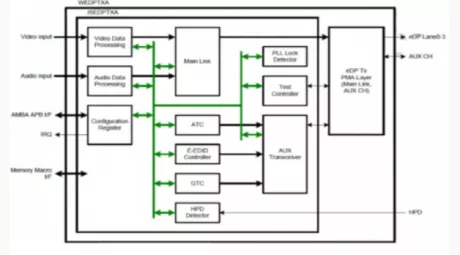

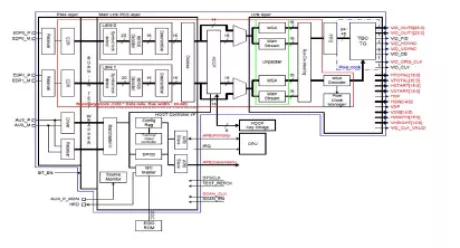

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 12FFC

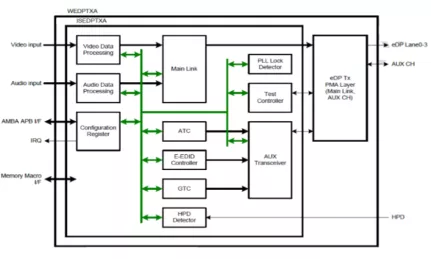

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channel

-

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in TSMC 40LP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength

-

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in UMC 55SP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength

-

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in UMC 55SP

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channel

-

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 40LP

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channe

-

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in UMC 40SP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength

-

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in UMC 40SP

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channel