DisplayPort Transceiver IP

Filter

Compare

13

IP

from

5

vendors

(1

-

10)

-

DisplayPort Intel® FPGA IP Core

- Intel now offers a fully VESA-compliant DisplayPort Intel® FPGA IP core v1.4

- The DisplayPort IP core is found prevalently in many video-related products servicing a wide variety of applications and has the following features:

-

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC 28HPC+, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC 12FFC, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC N7, 1.8V, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC N6, 1.8V, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

DisplayPort TX v2.1, 20Gbps x4-lane, TSMC N6, 1.8V, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

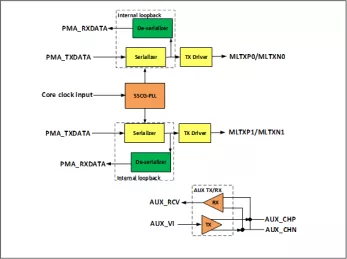

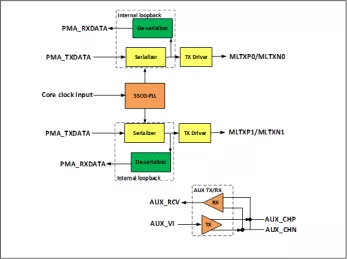

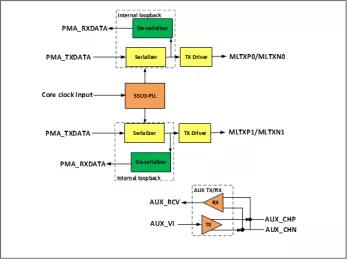

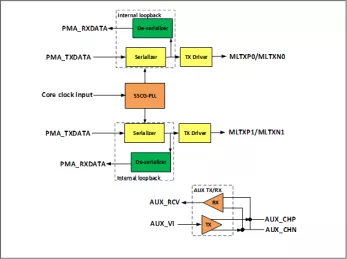

Display Port 2-Lane Transmitter PHY

- Compact IP size and easy for integration

- Ultra low power consumption for DisplayPort v1.2

- Extensive testability including loopback mode

-

Virtex-6 FPGA GTX Transceiver Wizard

- Creates customized HDL wrappers to configure high-speed serial transceivers

- Predefined protocol templates support Aurora (8B/10B and 64B/66B), Common Packet Radio Interface (CPRI™), DisplayPort, Fibre Channel, Gigabit Ethernet, High-Definition Serial Digital Interface (HD-SDI), 3 Gb/s Serial Digital Interface (3G-SDI), Interlaken, Open Base Station Architecture Initiative (OBSAI), OC-48, PCI EXPRESS® (PCIe®) generation I and II, Serial Advanced Technology Attachment (SATA) 1.5 Gb/s, SATA 3 Gb/s, Serial RapidIO generation I and II, 10 Gb Attachment Unit Interface (XAUI), and RXAUI-Dune Networks

- Automatically configures analog settings

-

Spartan-6 FPGA GTP Transceiver Wizard

- Creates customized HDL wrappers to configure high-speed serial transceivers in 7 Series FPGAs

- Predefined templates support these protocols: CPRI™, DisplayPort, Gigabit Ethernet, High-Definition Serial Digital Interface (HD-SDI), Open Base Station Architecture Initiative (OBSAI), PCI EXPRESS ® (PCIe ®) generation I, Serial RapidIO, 10 Gb Attachment Unit Interface (XAUI), Aurora 8B/10B, Serial Advanced Technology Attachment (SATA) 1.5 Gb/s, and SATA 3 Gb/s

- Automatically configures analog settings

-

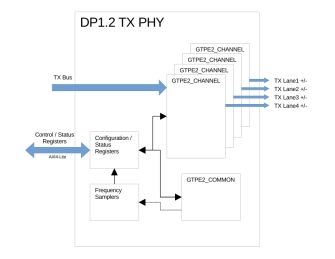

DisplayPort 1.2a TX PHY targeting 28nm Artix-7

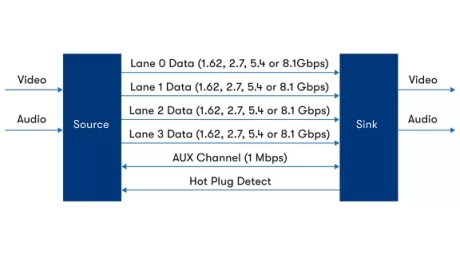

- Supported link rates of 1.62, 2.7 and 5.4 Gbps.

- Hardware proven.

- Simulation testbench.

- Example project, including firmware which performs link initialization with the PHY