DisplayPort 2.1 IP

Filter

Compare

32

IP

from

9

vendors

(1

-

10)

-

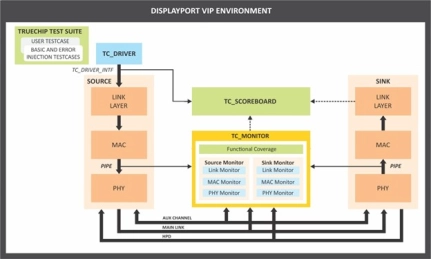

DisplayPort 2.1 Verification IP

- Supports Isochronous transport services over the Main-Link.

- Capable Link and device management services over the AUX_CH.

- Can handle AUX transaction to access the DisplayPort Configuration Data (DPCD) address.

- Capable of handling multi stream packet and single stream packet data transmission.

-

HDMI 2.1/ DisplayPort 2.1 Tx PHY TSMC N3P 1.2V, North/South Poly Orientation

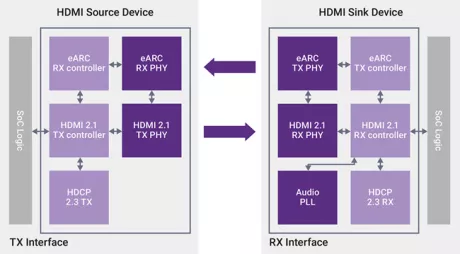

- HDMI 2.1 TX IP solution includes PHYs, controllers, HDCP embedded security modules, and verification IP

- Compliant with the HDMI 2.1, 2.0, 1.4, and HDCP 2.3, 1.4 specifications

- Support for key HDMI 2.1 features such as fixed-rate link capable of 48Gbps aggregate bandwidth, enhanced

- Metadata packets including dynamic HDR, eARC, auto low-latency mode, and variable refresh rate

-

HDMI 2.1/ DisplayPort 2.1 Tx PHY SS SF4X, North/South Poly Orientation

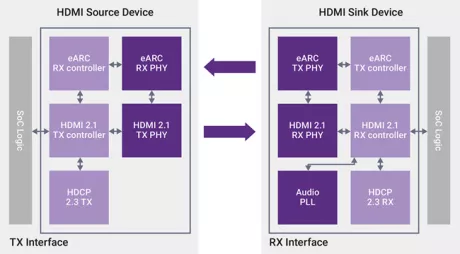

- HDMI 2.1 TX IP solution includes PHYs, controllers, HDCP embedded security modules, and verification IP

- Compliant with the HDMI 2.1, 2.0, 1.4, and HDCP 2.3, 1.4 specifications

- Support for key HDMI 2.1 features such as fixed-rate link capable of 48Gbps aggregate bandwidth, enhanced

- Metadata packets including dynamic HDR, eARC, auto low-latency mode, and variable refresh rate

-

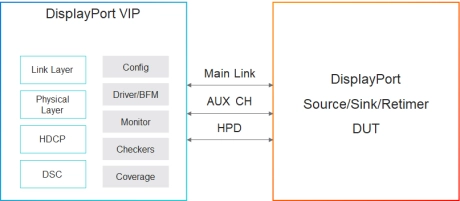

Simulation VIP for DisplayPort

- Device Support

- Source, Sink, Link Training-Tunable PHY Repeater (LTTPR/retimer)

- Main Link Interface

- Serial, Parallel (10-bit, 20-bit, 40-bit)

-

DisplayPort Receiver IP

- Silicon proven on multiple ASIC and FPGA processes

- Capable of operating without a host CPU in low complexity applications

- Horizontal and vertical video delimiter signals with 1, 2 or 4 pixels per output cycle, supporting up to 16K resolution output; deep color and HDR support

- 1.62 to 8.1 Gbps link rate across 1, 2, or 4 lanes

-

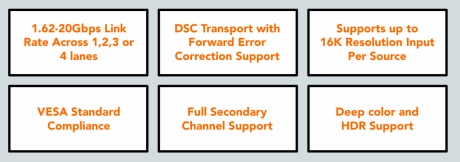

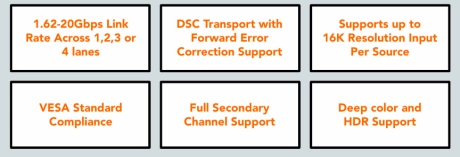

DisplayPort Transmitter IP

- Our 6th generation DisplayPort Transmitter Link Controller core supports DisplayPort 2.1, DisplayPort 1.4a and embedded DisplayPort 1.5.

- Features include link rates up to 20Gbps for DisplayPort 2.0, 8.1Gbps for DisplayPort 1.4a. Display Steam Compression (DSC), multi-stream transport (MST) and more. The base core includes all required link functionality— Main Link, Secondary Channel, and AUX Channel protocols—and supports the HDCP 2.3 standards for data encryption.

-

HDCP 2 on HDMI / DisplayPort Embedded Security Module Firmware (generation 3)

- Complete, self-contained security modules with hardware Root of Trust

- Transmitter (TX), Receiver (RX) and Repeater (Rep) solutions

- Silicon-proven. Widely deployed. Certified.

- Compliant with the latest HDCP 2.3 content protection standard (backwards compatible with HDCP 2.2)

-

4-port Receiver/Transmitter/Repeater HDCP 2.3 on HDMI 2.0 and/or DisplayPort 2.0/1.4 ESM (generation 3)

- The Multiport/Multiprotocol HDCP 2.2/2.3 Embedded Security Modules (ESMs) are autonomous modules that provide designers with complete and robust transmitter (TX), receiver (RX) and repeater (Rep) implementations of the HDCP 2.3 content protection technology over HDMI 2.1/2.0, DisplayPort 2.0/1.4, and USB 3.x Type-C wired connections.

- These solutions help designers shorten development cycles and fully meet the stringent security requirements of the DCP LLC licensing authority.

-

2-port Receiver/Transmitter/Repeater HDCP 2.3 on HDMI 2.0 and/or DisplayPort 2.0/1.4 ESM (generation 3)

- Complete, self-contained security modules with hardware Root of Trust

- Transmitter (TX), Receiver (RX) and Repeater (Rep) solutions

- Silicon-proven. Widely deployed. Certified.

- Compliant with the latest HDCP 2.3 content protection standard (backwards compatible with HDCP 2.2)

-

1-port Receiver/Transmitter HDCP 2.3 on HDMI 2.0 or DisplayPort 1.4/2.0 ESM (generation 3)

- The Multiport/Multiprotocol HDCP 2.2/2.3 Embedded Security Modules (ESMs) are autonomous modules that provide designers with complete and robust transmitter (TX), receiver (RX) and repeater (Rep) implementations of the HDCP 2.3 content protection technology over HDMI 2.1/2.0, DisplayPort 2.0/1.4, and USB 3.x Type-C wired connections.

- These solutions help designers shorten development cycles and fully meet the stringent security requirements of the DCP LLC licensing authority.