HDMI 2.1/ DisplayPort 2.1 Tx PHY TSMC N3P 1.2V, North/South Poly Orientation

The HDMI 2.1 TX Controller and PHY IP solutions, compliant with the HDMI 2.1 specification, provide the necessary logic to implem…

Overview

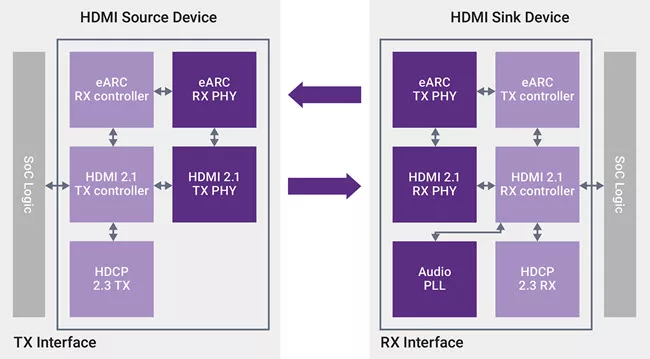

The HDMI 2.1 TX Controller and PHY IP solutions, compliant with the HDMI 2.1 specification, provide the necessary logic to implement and verify designs for various HDMI-based applications. The IP provides quality digital video and audio transmission with up to 48Gbps aggregate bandwidth for uncompressed 8K resolution at 60Hz refresh rate. It supports key features of HDMI 2.1 including dynamic HDR and enhanced audio return channel (eARC), ensuring higher frame-by-frame video quality and most advanced audio formats.

The power- and area-optimized HDMI 2.1 IP solutions encompass a suite of configurable digital controllers, High-Bandwidth Digital Content Protection (HDCP) embedded security modules (ESMs), high-speed mixed-signal PHYs, PLL, verification IP, IP Prototyping Kits, Linux software drivers, and IP subsystems. The highly efficient HDCP 2.3 on HDMI ESMs are designed to protect premium audio-visual content against unauthorized copying, interception, and tampering while meeting stringent security specification requirements.

Having all necessary design blocks for the HDMI subsystem, the IP solution enables system-on-chip (SoC) designers to lower integration risk and accelerate time-to-market.

Key features

- HDMI 2.1 TX IP solution includes PHYs, controllers, HDCP embedded security modules, and verification IP

- Compliant with the HDMI 2.1, 2.0, 1.4, and HDCP 2.3, 1.4 specifications

- Support for key HDMI 2.1 features such as fixed-rate link capable of 48Gbps aggregate bandwidth, enhanced

- Metadata packets including dynamic HDR, eARC, auto low-latency mode, and variable refresh rate

- Optimized for low power and small area

- Timing hardened blocks simplify placement and design closure

- Configurable controller architecture optimized for power, performance, and area

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 3nm | N3P | — |

Specifications

Identity

Provider

Learn more about Displayport IP core

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

DisplayPort 2025: Navigating the Next Wave of Display Innovation

Audio Transport in DisplayPort VIP

DisplayPort 2.1 vs DisplayPort 1.4: A Detailed Comparison of Key Features

Frequently asked questions about DisplayPort IP cores

What is HDMI 2.1/ DisplayPort 2.1 Tx PHY TSMC N3P 1.2V, North/South Poly Orientation?

HDMI 2.1/ DisplayPort 2.1 Tx PHY TSMC N3P 1.2V, North/South Poly Orientation is a Displayport IP core from Synopsys, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Displayport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Displayport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.