DDR controller/PHY IP

Filter

Compare

286

IP

from

24

vendors

(1

-

10)

-

DDR PHY & DDR Controller IP

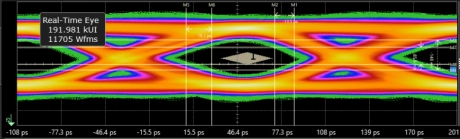

- DDR4/DDR3/DDR2 PHY IP fully compliant with the DFI 4.0 Specification.

- LPDDR5/LPDDR4/LPDDR3/LPDDR2 PHY IP fully compliant with the DFI 4.0 Specification.

- Support speeds up to 4266Mbps.

- IP is split into 2 hard macros.

-

SDRAM DDR Controller

- Dolphin Technology offers high performance DDR4/3/2 SDRAM and LPDDR5/4x/4/3/2 SDRAM Memory Controller IP across a broad range of process technologies.

-

MRDIMM DDR5 & DDR5/4 PHY & Controller

- The DDR IP Mixed-Signal MRDIMM DDR5 PHY and DDR5/4 Combo PHY provide turnkey physical interface solutions for ICs requiring access to JEDEC compatible SDRAM or MRDIMM/ RDIMM/ LRDIMM/ UDIMM DDR5 devices

- It is optimized for low-power and high-speed applications with robust timing and small silicon area

- It supports all JEDEC DDR5/4 SDRAM components in the market

-

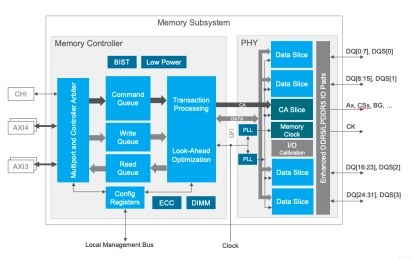

DDR Controller

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 and DDR5/4/3 protocol memories

- Memory controller interface complies with DFI standards up to version 5.0

- Priority per command on Arm® AMBA® 4 AXI, AMBA 3 AXI

- Single and multi-port host interface options

- QoS features allow command prioritization on Arm AMBA 4 AXI and CHI interfaces

- Silicon proven and shipping in volume

-

DDR Controller supporting DDR5 with Advanced Features Package

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling

-

DDR Controller supporting DDR5 with a CHI interface and Advanced Feature Package

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling

-

DDR Controller supporting DDR5 MRDIMM Gen2 with Advanced Features Package

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling

-

DDR Controller supporting DDR5 and DDR4 with Advanced Features Package

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling

-

DDR Controller supporting DDR5 and DDR4 with a CHI interface and Advanced Feature Package

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling

-

DDR Controller supporting DDR5 and DDR4 with a CHI interface

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling