D2D PHY IP

Filter

Compare

20

IP

from

15

vendors

(1

-

10)

-

-

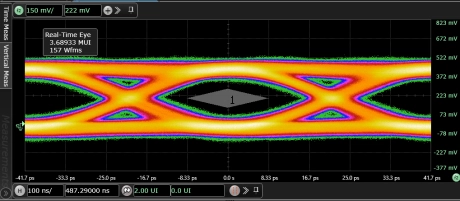

40G UltraLink D2D PHY

- Innovative mixed-signal architecture to achieve high bandwidth, ultra low latency and low power

- Flexible data rate from 20Gbps to 40Gbps

- Built-in self-test features to ensure “known good die”

- Interoperable between different technology nodes and foundries

- Easy routing and straightforward integration

- Achieves better than 10-15 bit error rate (BER) without requiring forward error correction (FEC)

- Integrated scrambling and lane de-skew functionality

- Supports -40ºC to 125ºC industrial temperature range

-

D2D Controller addon for D2D SR112G PHY with CXS interface

- Low Latency controller for die-to-die connectivity

- Supports PAM-4 and NRZ PHY signaling mode in all data rates

- Reduces BER with optional FEC configurations

- Supports Arm® AMBA® CXS interface

-

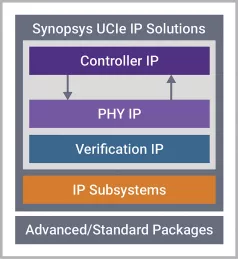

Universal Chiplet Interconnect Express PHY IP - GLOBALFOUNDRIES® 22FDX®

- Delivered as Hardmacro IP

- Implementation of the physical layer of the UCIe standard from Raw D2D Interface (RDI) to electrical interface of UCIe main band (MB) and sideband (SB)

- Includes TX and RX side

-

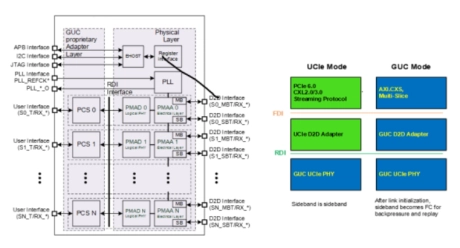

TSMC CLN5FF GUCIe LP Die-to-Die PHY

- IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package.

- This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the

-

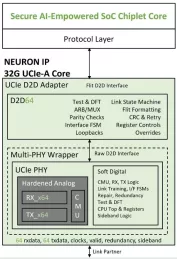

UCIe Chiplet PHY & Controller

- Compliant with the UCIe specification (2.0 & 1.1)

- Flexible Structure, easy to customize (Pre-hardened PHY tuned to Customer Spec, PHY + Adapter Layer, PHY + Adapter Layer + Customized Protocol Layer)

- Supports the CXS/AXI using the streaming package (AXI Interface bandwidth up to 89%)

-

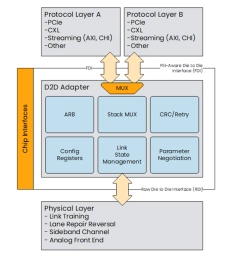

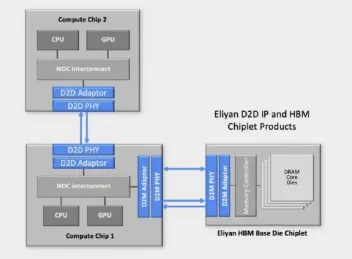

UCIe D2D Adapter

- The D2D Adapter for UCIe is a scalable adapter layer between one or more protocol components and the UCIe PHY, which ensures efficient data transfer across the UCIe Link by seamlessly coordinating with the Protocol Layer and Physical Layer.

- By minimizing logic on the main data path, it delivers a low-latency, optimized pathway for protocol Flits.

-

IPTD2D-A PHY and Controller

- Our mass production-proven IPTD2D-A D2D Interconnect IP Solutions offer industry-leading power efficiency, performance, and low latency, tailored for the next generation of high-performance computing, AI, and data center applications.

- With asynchronous “side-band” signals, the IPTD2D PHY can work at any frequency ranging from 2Gbps to 16Gbps, achieving the best balance between total bandwidth and power consumption.

-

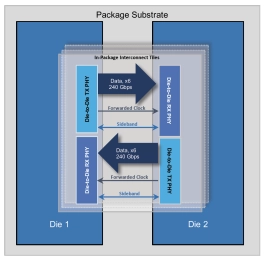

Die-to-Die PHY

- The NuLink technology delivers low-power and high-performance D2D IP core products, which support multiple industry standards and are available on both standard and advanced packaging.

-

Chiplet Interconnect - Die-to-die interconnect IP solutions for advanced and standard packaging applications

- High data rate of 2–24 Gb/s

- Very low power of < 0.375 pJ/bit @ 2–16 Gb/s 0.5-V VDDQ

- Very low latency of < 2 ns PHY-to-PHY

- Support for 2:1, 4:1, 8:1, 12:1 and 16:1 serialization and deserialization ratios