Convolutional Neural Network IP

Filter

Compare

12

IP

from

8

vendors

(1

-

10)

-

DPU for Convolutional Neural Network

- Configurable hardware architecture

- Configurable core number up to three

- Convolution and deconvolution

-

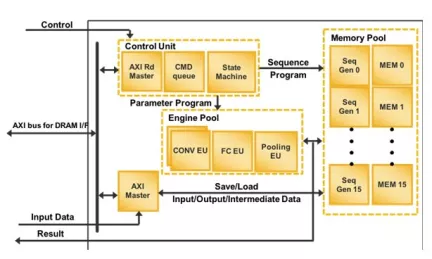

Convolutional Neural Network (CNN) Compact Accelerator

- Support convolution layer, max pooling layer, batch normalization layer and full connect layer

- Configurable bit width of weight (16 bit, 1 bit)

-

Accelerator for Convolutional Neural Networks

- Include VGG, ResNet, MobileNet, and other custom use cases.

-

Neural network processor designed for edge devices

- High energy efficiency

- Support mainstream deep learning frameworks

- Low power consumption

- An integrated AI solution

-

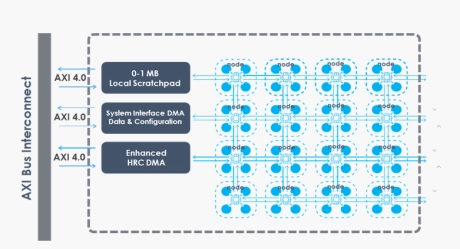

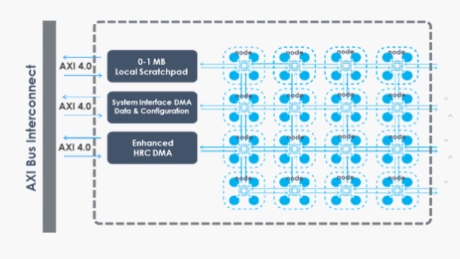

Run-time Reconfigurable Neural Network IP

- Customizable IP Implementation: Achieve desired performance (TOPS), size, and power for target implementation and process technology

- Optimized for Generative AI: Supports popular Generative AI models including LLMs and LVMs

- Efficient AI Compute: Achieves very high AI compute utilization, resulting in exceptional energy efficiency

- Real-Time Data Streaming: Optimized for low-latency operations with batch=1

-

IP Platform for BLE 5.2 and 802.15.4 IoT Sensors

- LE 5.2 CONTROLLER :

- IEEE 802.15.4 CONTROLLER :

- NEURAL NETWORK PROCESSOR :

- SENSOR FUSION :

-

IP Platform for AI-Enabled IEEE 802.15.4 Smart Sensors

- IEEE 802.15.4 CONTROLLER :

- NEURAL NETWORK PROCESSOR :

- SENSOR FUSION :

- SECURITY ACCELERATOR :

-

ARC EV Processors are fully programmable and configurable IP cores that are optimized for embedded vision applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

Neuromorphic Processor IP

- Supports 4-, 2-, and 1-bit weights and activations

- Supports multiple layers simultaneously

- Convolutional Neural Processor (CNP) and

- Fully-connected Neural Processor (FNP)

-

Neuromorphic Processor IP (Second Generation)

- Supports 8-, 4-, and 1-bit weights and activations

- Programmable Activation Functions

- Skip Connections

- Support for Spatio-Temporal and Temporal Event-Based Neural Network