CPRI IP

Filter

Compare

123

IP

from

17

vendors

(1

-

10)

-

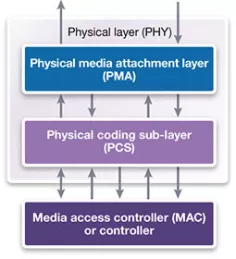

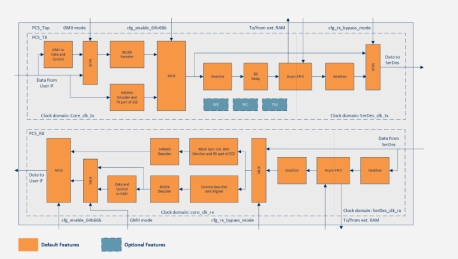

Ethernet PCS 1G/2.5G/5G/10G/25G & CPRI 7.0

- A combined silicon agnostic implementation of the PCS layer compliant with Ethernet standard IEEE 802.3-2018 and CPRI Specification V7.0 based solution

- The IP-core supports 1G, 2.5G, 5G, 10G, and 25G Ethernet data rates as well as CPRI data rate option 1 (614.14M) to option 10 (24.33024G).

-

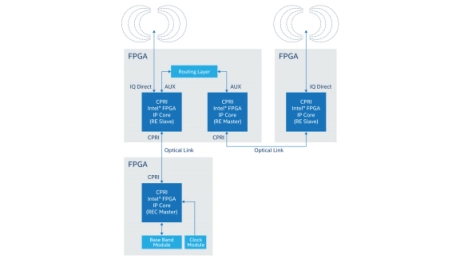

CPRI Altera® FPGA IP

- The Common Public Radio Interface (CPRI) Altera® FPGA IP core implements the CPRI Specification V7.0

- CPRI is a high-speed serial interface for network radio equipment controllers (REC) to receive data from and provide data to remote radio equipment (RE)

- The IP core targets high-performance, remote radio network applications

-

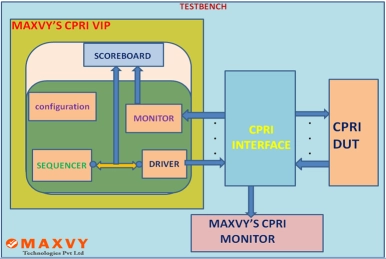

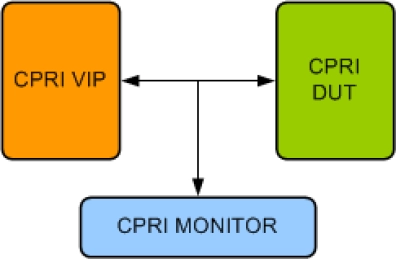

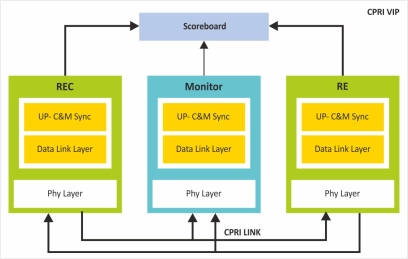

CPRI verification IP

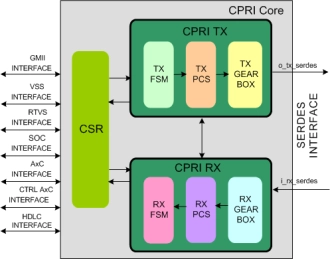

- The vendor provides configurable CPRI TX/RX verification IP

- The CPRI verification IP is fully compatible with CPRI version v7.0 with backward compatibility to previous versions and provides an efficient and effective way to verify the component interfacing with CPRI interface of an IP

-

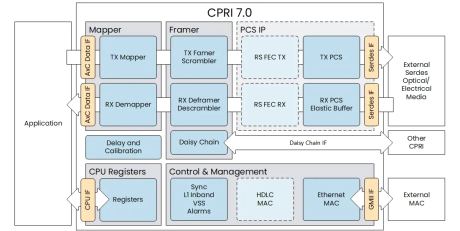

CPRI 7.0

- The Common Public Radio Interface (CPRI) 7.0 core is a silicon agnostic implementation of the CPRI 7.0 specification, which is targeting both ASIC and FPGAs CPRI.

- CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems.

- With its extreme flexibility and reduced logic consumption, the CPRI 7.0 IP core is the perfect match whether the application is REC (Radio Equipment Controller) or RE (Radio Equipment).

-

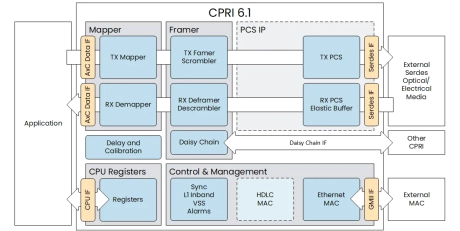

CPRI 6.1

- Common Public Radio Interface (CPRI) 6.1 core is a silicon agnostic implementation of the CPRI 6.1 specification, which is targeting both ASIC and FPGAs.

- CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems.

-

CPRI Verification IP

- Compliant with CPRI Specification V4.2/V5.0/V6.0/V6.1/V7.0

- Complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

-

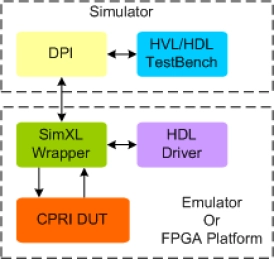

CPRI Synthesizable Transactor

- Compliant with CPRI Specification V4.2, V5.0, V6.0, V6.1 and V7.0.

- Supports complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

-

CPRI CONTROLLER IIP

- Compliant with CPRI Specification V4.2, V5.0, V6.0, V6.1 and V7.0.

- Complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

-

CPRI Verification IP

- Fully compliant to CPRI specification V7.0 with backward compatibility

- Supports following line bit rates of CPRI specifications

- 614.4 Mbit/s, 1228.8 Mbit/s, 3072.0 Mbit/s, 4915.3 Mbit/s, 6144.0 Mbit/s, 9830.4 Mbit/s, 8110.08 Mbit/s, 10137.6 Mbit/s, 12165.12Mbit/s

- 614.4 Mbit/s, 1228.8 Mbit/s, 3072.0 Mbit/s, 4915.3 Mbit/s, 6144.0 Mbit/s, 9830.4 Mbit/s, 8110.08 Mbit/s, 10137.6 Mbit/s, 12165.12Mbit/s

- Supports 8B/10B and 64B/66B line coding and scrambling/ descrambling and RSFEC.

-

12G CPRI PHY - TSMC N5 x4 1.2V North/South (vertical) poly orientation

- Supports 1.25 to 16 Gbps data rates

- Supports PCI Express,IEEE 802.3, SGMII and QSGMII,SATA, CEI-6G and CEI-11G, Serial Rapid IO (SRIO), CPRI, OBSAI, JESD204B

- Supports x1 to x16 macro configurations