BCH Decoder IP

Filter

Compare

51

IP

from

17

vendors

(1

-

10)

-

NavIC BCH Decoder

- Compliant with 'ISRO-NAVIC-ICD-SPS-L1-1.0' standard [1].

- Supports the BCH decoding for subframes 1 (TOI) signal.

- Throughput matching the required specifications.

- Bit-error-rate and block-error-rate performance meet the required specifications.

-

DVB-S2X Wideband LDPC/ BCH Decoder

- The DVB-S2X Wideband LDPC Decoder is a powerful FEC core decoder for Digital Video Broadcasting via Satellite.

- It implements extensions to the DVB-S2 design for better performance and efficiency as well as robust service availability.

-

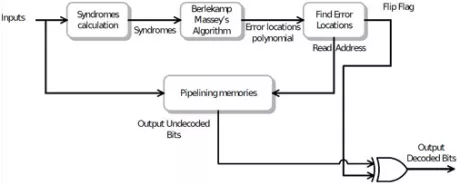

UltraFast BCH Decoder

- BCH codes are widely used where bit errors are scattered randomly within the codeword. The Ultrafast BCH Decoder is capable of processing an entire BCH codeword per clock cycle in a pipelined way. Therefore, tt achieves outstanding data rates.

- The design can be parameterized at design-time to support different codeword sizes and code rates. Latency can be adjusted by insertion or removal of pipeline register stages.

-

DVB-T2 Demodulator and LDPC/ BCH Decoder

- DVB-T2 EN302 755 V1.2.1, Rev.9 compliant

- Supports IF input

- Single input – Single output (SISO)

- Sampling frequency offset (SFO) tracking and compensation

- Carrier frequency offset (CFO) detection and correction

-

DVB-S2 LDPC BCH Decoder and Encoder

- The DVB-S2 LDPC-BCH block is a powerful FEC (Forward Error Correction) subsystem for Digital Video Broadcasting via Satellite.

- In Digital video broadcasting for digital transmission for satellite applications, a powerful FEC sub-system is needed. FEC is based on LDPC (Low Density Parity Check) codes concatenated with BCH (Bose Chaudhuri Hocquenghem) codes, allowing Quasi Error Free operation close to the Shannon limit.

-

DVB-S2X LDPC/ BCH Decoder

- The DVB-S2X LDPC Decoder is a powerful FEC core decoder for Digital Video Broadcasting via Satellite.

- It implements extensions to the DVB-S2 design for better performance and efficiency as well as robust service availability.

-

BCH Decoder IP

- BCH decoder compliant with the DVB-T2/S2 standard.

- Available for Altera/Xilinx FPGA or ASIC implementation.

- High speed design.

- BCH decoder works on GF(2M) where M = 16 or 14 and correctup to T errors where T = 10 or 12.

-

-

DVB-C2 Receiver (including LDPC and BCH decoder)

- Compliant with ETSI 302 769 (DVB-C2).

- Support for short blocks (16200 bits) and long blocks (64800 Bits).

- Support for all modulation schemes (16-QAM, 64-QAM, 256-QAM, 1024-QAM, 4096-QAM).

- Support for all interleaving schemes of all modulation schemes.