ARC IP

Filter

Compare

3,328

IP

from

271

vendors

(1

-

10)

-

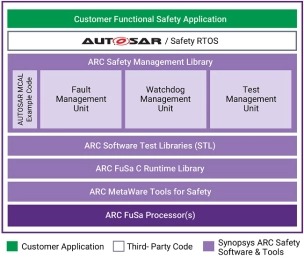

ARC Functional Safety Software

- The functional safety (FuSa) software components in conjunction with Synopsys’ ASIL certified MetaWare Development Tools for Safety and industry leading ARC® FS processors provide comprehensive ASIL compliant solutions which dramatically reduce customers’ risk and SoC certification effort.

-

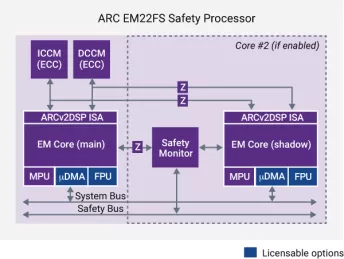

ARC EM22FS safety processor

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Single solution support for safety level up to ASIL D; Supports both ASIL D lockstep operation or ASIL B single core operation

- Includes hardware safety features such as ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

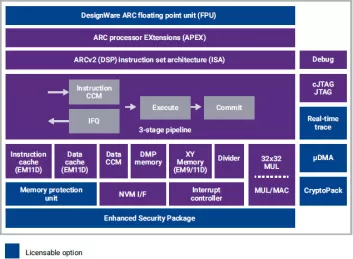

ARC EM9D 32-bit DSP Enhanced Processor core based on the ARCv2DSP ISA with CCM and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

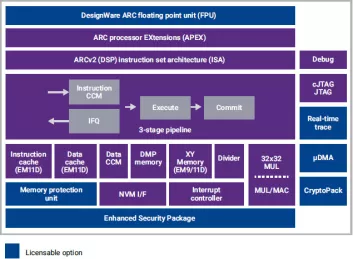

ARC EM11D Enhanced 32-bit processor core, ARCv2DSP ISA with Cache and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

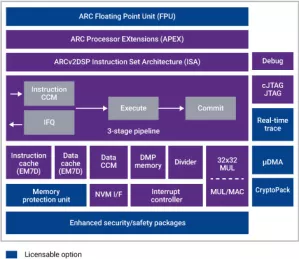

ARC EM7D DSP Enhanced 32-bit processor core with caches, ARCv2DSP ISA, for low power embedded DSP ap

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

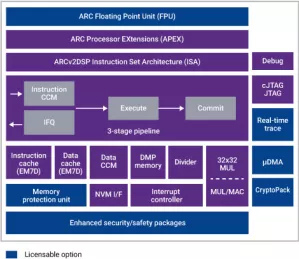

ARC EM5D Enhanced 32-bit processor core, ARCv2DSP ISA, for low power embedded DSP applications

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

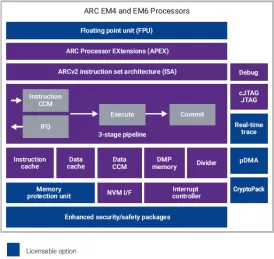

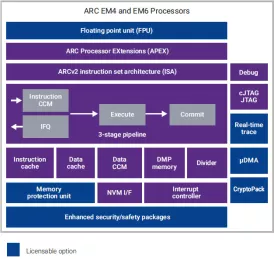

ARC EM6 32-bit processor core with cache for embedded applications

- Very small size - 0.01mm2 (28 HPM)

- 1.81 DMIPS/MHz performance, 4.18 CoreMarks/MHz

- Up to 240 interrupts with 16 levels

- 512B - 2MB instruction closely coupled memory (ICCM)

-

ARC EM4 32-bit processor core, ARC V2 ISA, for embedded applications

- Very small size - 0.01mm2 (28 HPM)

- 1.81 DMIPS/MHz performance, 4.18 CoreMarks/MHz

- Up to 240 interrupts with 16 levels

- 512B - 2MB instruction closely coupled memory (ICCM)

-

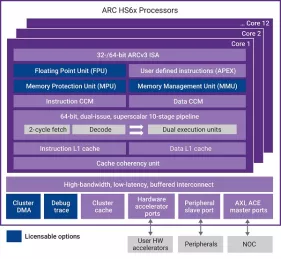

Scalar and SIMD floating point option for the ARC HS5x, HS5xD and HS6x processors

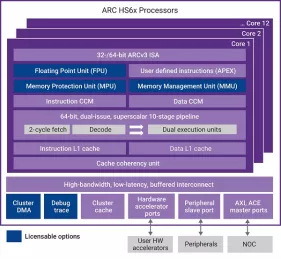

- Dual-issue, 64-bit processors for high-performance embedded applications

- 52-bit physical and 64-bit virtual addressing

- Up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

-

Memory management unit (MMU) option for ARC HS5x and HS6x processors

- Dual-issue, 64-bit processors for high-performance embedded applications

- 52-bit physical and 64-bit virtual addressing

- Up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators