AMBA IP

Filter

Compare

1,136

IP

from

100

vendors

(1

-

10)

-

Verification IP for AMBA ATB

- Trace Data Transfer (Valid, ready signaling)

- Narrow Trace Data Transfer (Data Valid Bytes signaling)

- Flow Control (Valid, ready signaling)

- Flush Request Response (Flush Valid, Ready signaling with Data transfer)

-

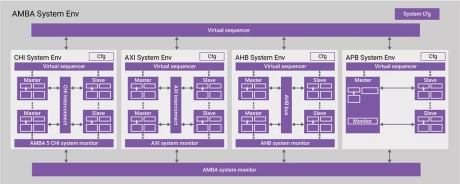

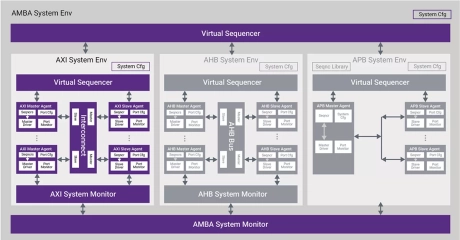

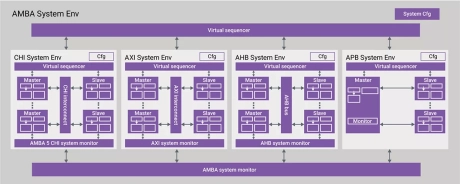

Verification IP for AMBA AXI

- Complete protocol support for AXI5, AXI-J/K, AXI4, AXI4-Lite, AXI3

- Programmable number of Managers, Subordinates, and Port Monitors

- Interconnect model

- System Monitor

-

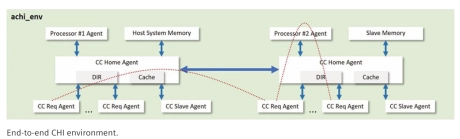

Verification IP for Arm AMBA CHI Protocol

- AMBA 5 CHI-A/B/C/D/E/F/G

- Request node, secondary node agents and monitor

- Complete port-level checks

- Supports all interface types

-

Verification IP for AMBA APB

- Native SystemVerilog/Verilog with UVM

- Includes primary, secondary, monitor

- Runs natively on all major simulators

- Built-in UVM sequence library

-

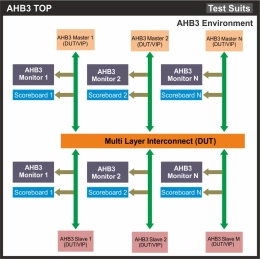

Verification IP for AMBA AHB

- Complete protocol support for AHB5, AHB3, AHB2, AHB-Lite, and AHB Multi Layer

- Includes primary, secondary, monitor

- Configurable bus model

- Backdoor access to AHB secondary memory

-

Verification IP for Arm AMBA ACE Protocol

- Complete protocol support for AMBA ACE 5, H, J and K, ACE4, ACE-Lite, AXI5, AXI4, AXI4-Lite, and AXI3.

- Configurable interconnect model for AXI5, AXI4, AXI, ACE5, and ACE4

- Backdoor access to ACE primary cache

-

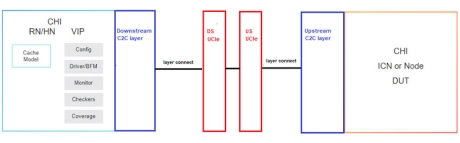

Simulation VIP for AMBA CHI-C2C

- Incorporating the latest protocol updates, the Cadence Verification IP for CHI-C2C provides a complete bus functional model (BFM), integrated automatic protocol checks, and a coverage model.

- Designed for easy integration in testbenches at IP, systems with multiple CPUs, accelerators, or other device chiplets, the VIP for CHI-C2C provides a highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms.

-

AMBA AHB 3 Lite Verification IP

- The AMBA 3 AHB-Lite Verification IP provides an effective & efficient way to verify the components interfacing with AMBA®3 AHB-Lite bus of an IP or SoC.

- The AMBA 3 AHB-Lite VIP is fully compliant with standard AMBA 3 AHB-Lite specification from ARM.

- This VIP is a light weight VIP with easy plug-andplay interface so that there is no hit on the design cycle time.

-

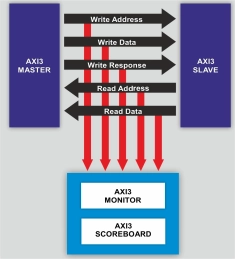

AMBA AXI3 Verification IP

- The AMBA AXI3 Verification IP provides an effective & efficient way to verify the components interfacing with AMBA® AXI3 bus of an IP or SoC.

- The AMBA AXI3 VIP is fully compliant with standard AMBA® AXI3 specification from ARM.

- This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design cycle time.

-

Verification IP for AMBA

- AMBA® ACE and CHI coherent interconnect technologies enable an entirely new class of high-performance datacenter applications in areas of machine learning, network processing, storage off-load, in-memory database, and 4G/5G wireless technology.

- Processor architectures and accelerators can now seamlessly operate over cache coherent intercon nects using the right combination of general-purpose processors and heterogeneous acceleration devices, such as FPGAs, GPUs, network/ storage adapters, intelligent networks, and custom ASICs.