7nm LPDDR5X PHY IP

Filter

Compare

2

IP

from

2

vendors

(1

-

2)

-

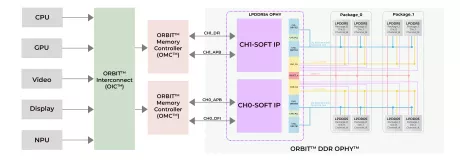

LPDDR5X/5/4X/4 combo PHY at 7nm

- Compliant with JEDEC JESD209-5B for LPDDR5X/5/4X/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

-

LPDDR5X Secondary/Slave (memory side!) PHY

- JEDEC standard LPDDR5X @ 8533Mbps (Mbits per second per pin)

- Flexible channel architecture – 16- or 32-bit data path widths, supporting either single x32 channel or two x16 channels – 64-bit support, supporting two x32 channels

- Support for byte-mode DRAM devices for high capacity systems

- ZQ Calibration