64-Bit RISC-V IP

Filter

Compare

88

IP

from

17

vendors

(1

-

10)

-

Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex. Designed for a range of applications requiring maximum single thread performance in Linux-capable devices. Improved performance compared with Gen#1.

-

64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- 64-bit RISC-V core with in-order single issue pipeline based complex.

- Tiny Linux-capable processor optimized for low power and small area.

- Ideally fits IoT applications requiring Linux.

-

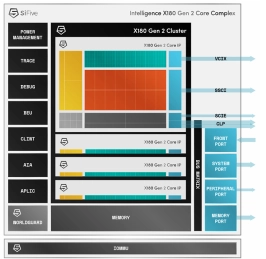

Multi-core capable 64-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X180 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 64-bit version, X100 series IP delivers higher performance and better integration with larger memory systems.

-

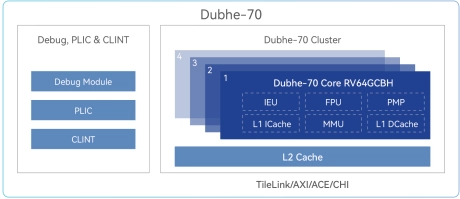

Ultra-low power consumption out-of-order commercial-grade 64-bit RISC-V CPU IP

- Dubhe-70 is a 9+ stage, 3-issue, out-of-order CPU IP that supports the rich RISC-V instruction set, RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop.

- With a score of 7.2 SPECInt2006/GHz, Dubhe-70 targets applications that require highly energy-efficient computation, including mobile, desktop, AI, and automotive.

-

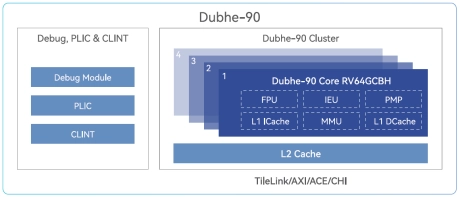

High Performance 64-bit RISC-V Processor

- Dubhe-90 is a high-performance commercial RISC-V CPU Core IP that is deliverable.

- It adopts an 11+ stage and 5-issue pipeline, superscalar, and deep out-of-order execution, and supports standard RISC-V RV64GCBH extensions.

-

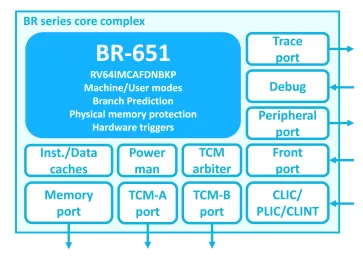

64-bit RISC-V high-performance embedded core

- 64-bit RISC-V high-performance embedded core. Ideal for control/compute/acceleration workloads requiring high performance and 64-bit capabilities.

-

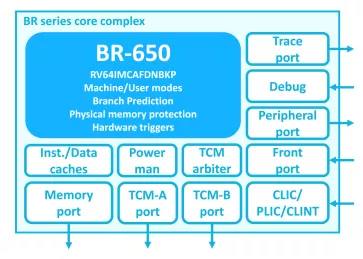

64-bit RISC-V embedded core with in-order single issue pipeline

- 64-bit RISC-V embedded core with in-order single issue pipeline.

- Optimized for low power and small area.

- Perfectly fits for embedded control.

-

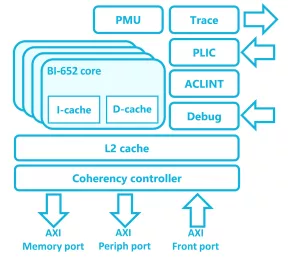

64-bit RISC-V core with in-order dual issue pipeline based complex for Linux-based systems

- 64-bit RISC-V core with in-order dual issue pipeline based complex.

- Balanced power efficiency and performance.

-

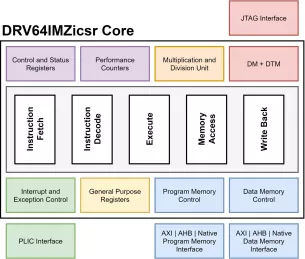

64-bit RISC-V CPU with M, Zicsr extensions and External Debug support

- Five-stage pipeline

- Harvard architecture

- RV64I Base RISC-V ISA

-

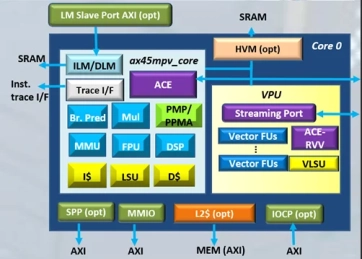

64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

- 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU)

- Symmetric multiprocessing up to 8 cores