5G NR LDPC IP

Filter

Compare

10

IP

from

5

vendors

(1

-

10)

-

LDPC Decoder for 5G NR and Wireless

- The 5G NR LDPC Decoder IP Core offers a robust solution for LDPC decoding, featuring a dedicated LDPC decoder block for optimal performance.

- It employs the Min-Sum LDPC decoding algorithm to ensure efficient decoding.

- The core allows for programmable internal bit widths at compile time, though the default values are usually sufficient.

-

5G LDPC Intel® FPGA IP

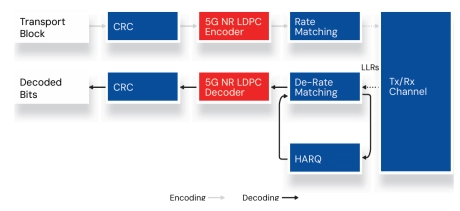

- Low-density parity-check (LDPC) codes are linear error correcting codes that help you to transmit and receive messages over noisy channels

- The 5G LDPC and LDPC-V Intel® FPGA IP implement LDPC codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration in your wireless design.

- LDPC codes offer better spectral efficiency than Turbo codes and support the high throughput for 5G new radio (NR).

-

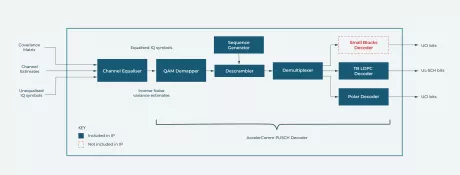

PUSCH Equalizer for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standards

- Improved spectral efficiency across low SINR range against industry-standard simulation toolbox

-

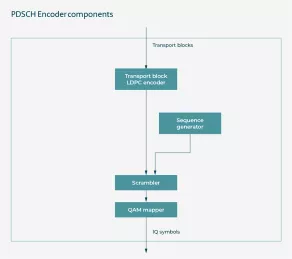

PDSCH Encoder for 3GPP 5G NR

- The PDSCH Encoder and PUSCH Decoder products simplify the creation of high performance 5G NR implementations.

- PDSCH Encoder features the new QAM mapper and Scrambler functionality. These are integrated with LDPC encoder chain and transport block chain components.

- PDSCH encoder has a configurable IQ parallelism for improved performance per clock.

- The functions included are CRC, Segmentation, LDPC encode, Rate matching, Integrated HARQ, Concatenation, Scrambling and Modulation.

-

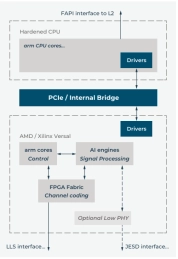

Modular, high performance 5G NR Layer 1 (PHY) solutions for Non-Terrestrial Network applications

- Complete implementation as per 3GPP standards and O-RAN SCF specifications.

- A full Layer 1 PHY designed and developed by AccelerComm™ using a mixture of hardware and software optimized to meet the needs of satellite vendors.

- Openly Licensable.

- Pre-integrated with AccelerComm™ LDPC and Polar encoder/decoder chains and inherits all the benefits from these highly performant products.

-

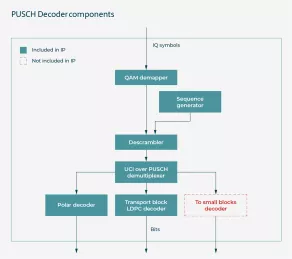

PUSCH Decoder for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standard

- Improved BLER for UCI control data

-

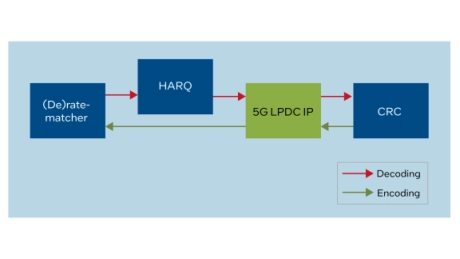

5G LDPC Encoder / Decoder

- CRC encoding

- Filler bits insertion/removal

- LDPC encoding (basegraph1 and 2, all Z-values)

-

LDPC Intel® FPGA IP

- Low-density parity-check (LDPC) codes are linear error correction codes that allow you to transmit messages over noisy channels.

- Intel's 5G Low-Density Parity Check (LDPC) Intel FPGA Intellectual Property (IP) core is a high-throughput encoder or decoder that is compliant with 3rd Generation Partnership Project (3GPP) 5G specification.

-

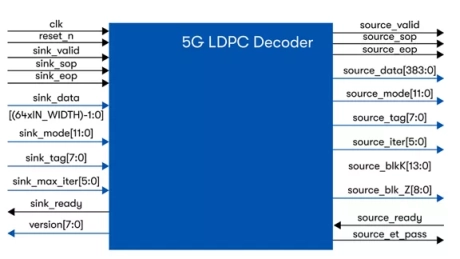

5G-NR LDPC Decoder

- High throughput

- Low-power and low-complexity design

- Block-to-block on-the-fly configuration

-

Flexible LDPC encoder/decoder

- Flexible LDPC codes, hundreds of codes can be handled simultaneously, run-time reconfigurable

- Supports expansion factor ranging from 2 to 1024