25G 50G Ethernet IP

Filter

Compare

16

IP

from

7

vendors

(1

-

10)

-

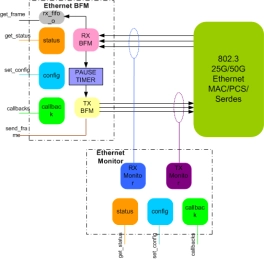

Ethernet 25G,50G Verification IP

- Supports 25G and 50G Speeds as per the 802.3-2018 specification,

- 25GBase_R

- 25GBase_KR

- 50GBase_KR

-

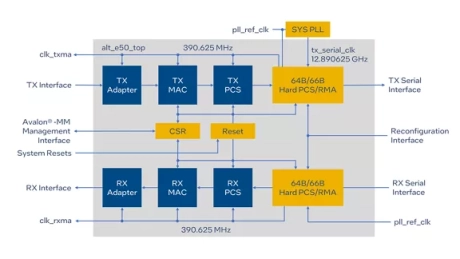

50G Ethernet Intel® FPGA IP

- The 50G Ethernet Intel® FPGA IP core implements the 25G & 50G Ethernet Specification, Draft 1.4 from the 25 Gigabit Ethernet Consortium and the IEEE 802.3by 25Gb Ethernet draft

- The IP core includes an option to support unidirectional transport as defined in Clause 66 of the IEEE 802.3-2012 Ethernet Standard

- The MAC client side interface for the 50 Gbps Ethernet IP core is a 128-bit Avalon® streaming interface (Avalon-ST)

-

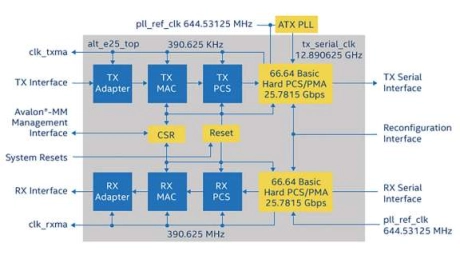

25G Ethernet Intel® FPGA IP

- This IP core implements the 25G and 50G Ethernet Specification, Draft 1.4 from the 25 Gigabit Ethernet Consortium

- The IP core includes an option to support unidirectional transport as defined in Clause 66 of the IEEE 802.3-2012 Ethernet Standard. The media access control (MAC) client side interface for the 25GbE IP core is a 64 bit Avalon® streaming interface (Avalon-ST)

- It maps to one 25.78125 Gbps transceiver

- The IP core optionally includes Reed-Solomon forward error correction (FEC) for support of direct attach copper (DAC) cable.

-

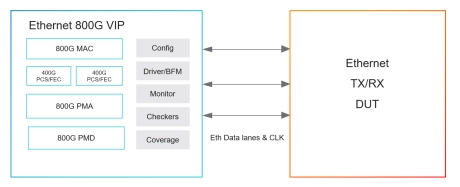

Simulation VIP for Ethernet up to 800G

- 800Gbps Interfaces

- 800Gbps Ethernet interfaces based on Ethernet Technology Consortium supports:

- 800GMII

- 800GBase-R Dual-PCS 32 lanes (25Gb/s)

-

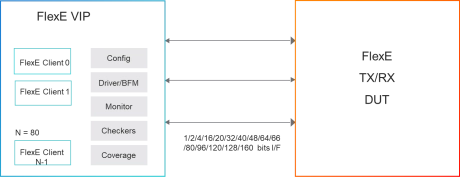

Simulation VIP for Ethernet FlexE

- OIF FLEXE-02.1(2019)

- Channelization/Bonding/Sub-Rating/Hybrid

- Multiple 50G/100G/200G/400G BaseR PHY

- FlexE clients of 5G, 10G, 25G, 40G, 50G, 100G, 200G, and 400G speeds

-

Ethernet TSN Verification IP

- Supports Time Sensitive transmission of data over Ethernet networks

- Full support for IEEE 802.1Qat

- Full support for IEEE 802.1QAV

- Full support for IEEE 802.1Q

-

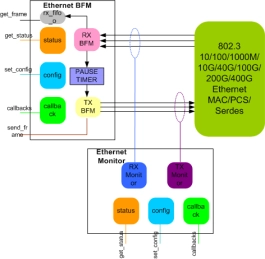

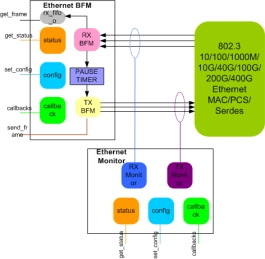

Ethernet - up to 800G Verification IP

- Supports 2.5G and 5G Speeds as per 802.3cb

- 2.5GBASE-KX

- 5GBASE-KR

- 2.5GBASE-T

-

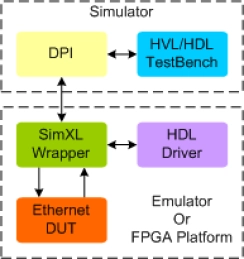

Ethernet Synthesizable Transactor

- Supports Full MII/RMII/SMII TX/RX functionality

- Supports Mac control and data frames support

- Ability to generate VLAN tagged and Priority tagged frames

- Supports Pause frame detection and generation

-

Enterprise Ethernet PCS IP

- Compliant with IEEE standards25G Consortium specifications for 25G & 50G r1.6 (Oct 15, 2015)

- Configurable for 10G, 25G, 40G, 50G and 100G Ethernet applications

- Integration tested with the Synopsys Enterprise Ethernet MAC and Multi-Protocol PHYs

- Comprehensive deliverables packaged in an IP-XACT compatible .run file