Simulation VIP for Ethernet FlexE

The Cadence® Verification IP (VIP) for Flexible Ethernet (FlexE) provides a mature, capable compliance verification solution for …

Overview

The Cadence® Verification IP (VIP) for Flexible Ethernet (FlexE) provides a mature, highly capable compliance verification solution for the FlexE protocol stack incorporating bus functional model (BFM) and integrated protocol checkers and coverage. The VIP for FlexE is designed for easy integration in test benches at IP, system-on-chip (SoC), and system levels helping to reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP for Ethernet FlexE is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

Supported specification: OIF FLEXE-02.1(2019) and IEEE 802.3-2018.

Key features

- OIF FLEXE-02.1(2019)

- Channelization/Bonding/Sub-Rating/Hybrid

- Multiple 50G/100G/200G/400G BaseR PHY

- FlexE clients of 5G, 10G, 25G, 40G, 50G, 100G, 200G, and 400G speeds

- Maximum number of FlexE clients supported: 80

- Maximum number of BaseR PHY supported: 8

- 5G and 25G granularity

- Calendar A/B

- Calendar Resizing

- Padding and Interleaving

- Management and Synchronization frames

- Skew/De-skew

- PMA Bus-Width

- 1, 2, 4, 10, 16, 20, 32, 40, 64, 66, 80, 120, 128, 160

- Frame Types

- Ethernet IEEE 802.3 (type and length defined)

- Jumbo frame

- MAGIC frame

- Version II frame

- Tagged Frames: Single Tagged (Q-VLAN tag) and Double tagged (S-VLAN tag and Q-VLAN tag)

- PTP

- MACSEC

- Custom Frame

- Proprietary header

- Clock

- Single Clock mode - External

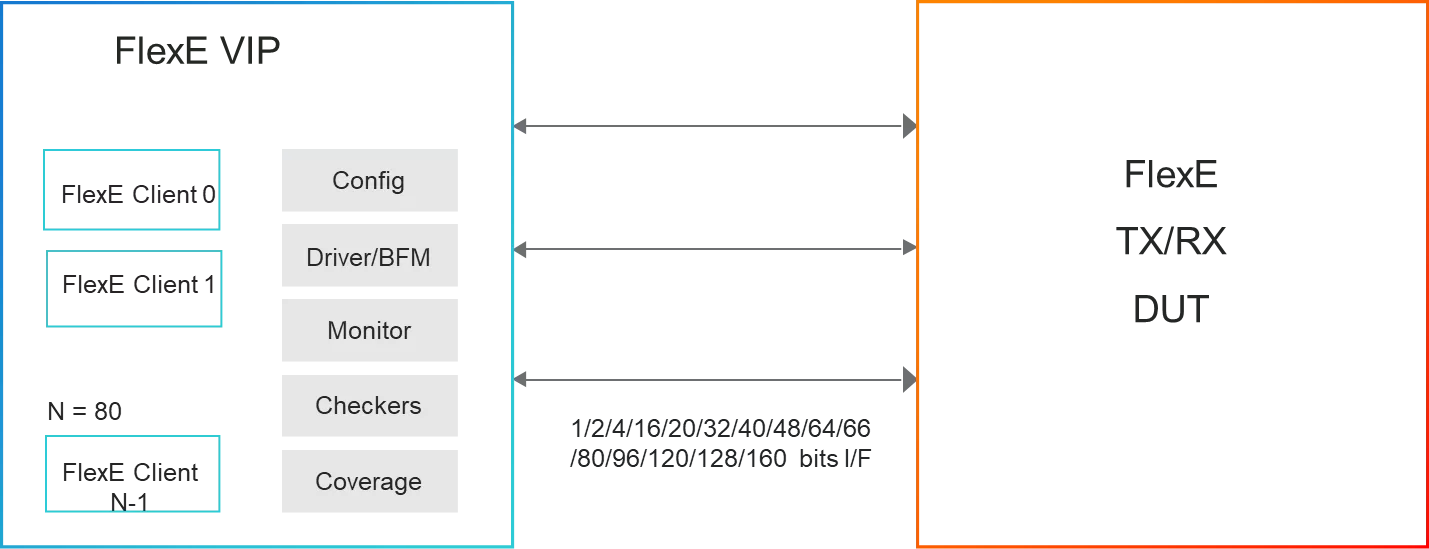

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Simulation VIP for Ethernet FlexE?

Simulation VIP for Ethernet FlexE is a Ethernet IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.