BitBLT Graphics Hardware Accelerator (AXI4 Bus)

The DB9100AXI4 BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from comma…

Overview

The DB9100AXI4 BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

The DB9100AXI4 also contains a Monochrome Bitmap Color Expansion feature, typically used for font expansion of compressed character bitmaps. A 1-bit depth bitmap is expanded to one of two colors, a foreground or background color, with the foreground color representing the text, and the background color the non-text background.

The DB9100AXI4 also contains a programmable Alpha Blend unit, blending two bitmaps into one.

The DB9100AXI4 interfaces to a microprocessor and frame buffer memory via the AMBA AXI4 Interconnect, providing high performance memory throughput. The DB9100AXI4 contains a DMA Command Linked-List Processing Unit, for independently reading and processing graphics commands from the host processor.

Key features

- Bit Block Transfer – 3 Independent Memory Sources of data:

- On-Screen & Off-Screen Data Block (SRC)

- Off-Screen Fixed Pattern Data Block (PTN)

- On-Screen visible Data Block (DST)

- Raster Operations (ROP) performed on Block Transfers:

- 256 Raster Operations

- ROP0, ROP1, ROP2, & ROP3 operations

- Includes industries most popular 16 ROPs

- BitBLT Draw Features:

- Pixels, Horizontal & Vertical Lines

- Overlapping & Non-Overlapping Block Transfers

- Solid Color Block Fills

- FONT Monochrome Bitmap to Color Expansion, either Transparent or Opaque

- Rotation Block Transfers: 0, 90, 180, 270 degrees

- Block Stretch on X & Y Axis

- Alpha Blending

- Sprite Moves

- Command FIFO or Link-List Display Processing Unit:

- Simplifies Processor Interface

- Minimizes Processor Overhead

- Frame Buffer & Display Features Supported:

- Display Resolutions 4K x 4K

- 4 GB Memory Range

- 8, 16 , 24, & 32 bits-per-pixel color depths

- Interrupt Controller with 3 sources of internal interrupts with masking control

- Reference Software Driver Included

- Reference Driver

- Graphics API Reference Design

- On-Chip Interconnect Compliance - AXI4:

- AMBA AXI4 Protocol Specification (V3.0)

- FPGA Integration Support:

- Altera Quartus II & Qsys Integration & ARM / NIOS II EDS Reference Design

- Xilinx Vivado IP Integrator & Reference Design

- ASIC / ASSP Design-In Support:

- Compliance to RTL Design, Coding, & Verification Standards

- Digital Blocks Support Services

- Compatible with Digital Blocks DB9000 Family of TFT LCD Controller IP Cores and Reference Designs

- Fully-synchronous, synthesizable Verilog RTL core.

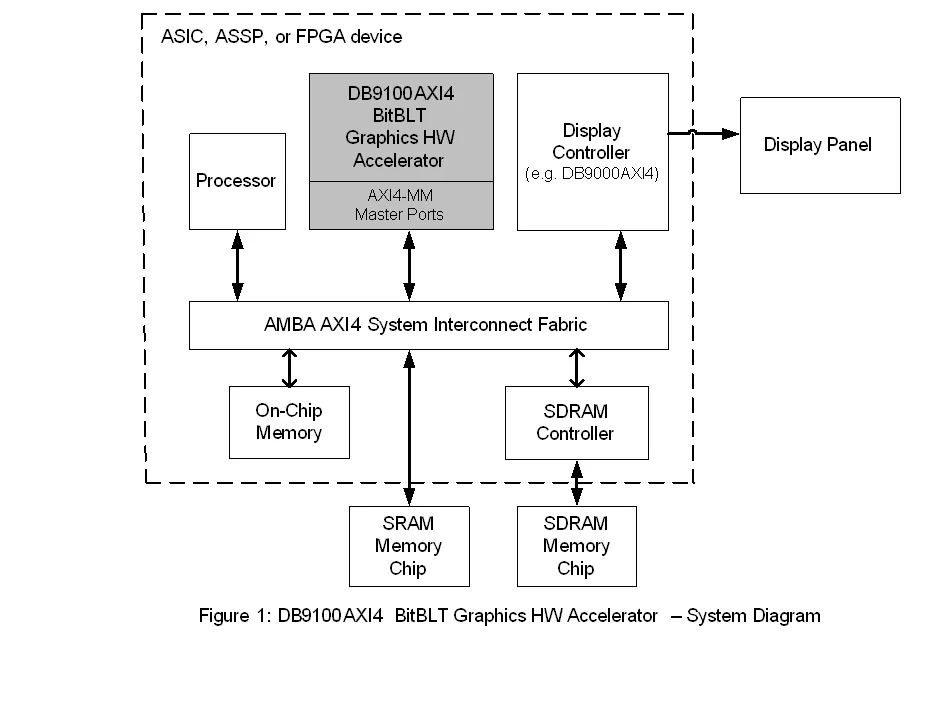

Block Diagram

Benefits

- The DB9100 family of BitBLT Graphics Hardware Accelerator IP Cores provides a higher graphics performance than a Host or GPU, while offering higher software productivity.

What’s Included?

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about GPU IP core

Tape-out Risk in the Age of Edge AI: The Case for GPU IP

Power, Not Area: Why Edge GPU Design Is Entering a New Era

What Does a GPU Have to Do With Automotive Security?

How Alternate Geometry Processing Enables Better Multi-Core GPU Scaling

Desktop-Quality Ray-Traced Gaming and Intelligent AI Performance on Mobile with New Arm Mali G1-Ultra GPU

Frequently asked questions about GPU IP cores

What is BitBLT Graphics Hardware Accelerator (AXI4 Bus)?

BitBLT Graphics Hardware Accelerator (AXI4 Bus) is a GPU IP core from Digital Blocks, Inc. listed on Semi IP Hub.

How should engineers evaluate this GPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.