OTP IP

Welcome to the ultimate OTP IP hub! Explore our vast directory of OTP IP

All offers in

OTP IP

Filter

Compare

1,091

OTP IP

from

7

vendors

(1

-

10)

-

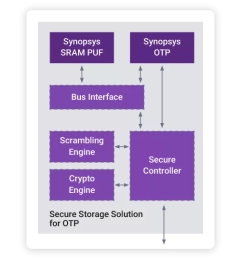

Secure Storage Solution for OTP IP

- Advanced Security: Encrypted storage in OTP using dynamic root key from SRAM PUF

- System-Level Security Extension: Add-on allows sharing the SRAM PUF to protect chip-level assets

- Flexible Security Configuration: Secure regions within OTP can be tailored to meet specific needs

-

GF 22FDX 5.5V OTP Auto-Grade1 IO Staggered

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

GF 22FDX 5.5V OTP Auto-Grade1 IO Inline

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

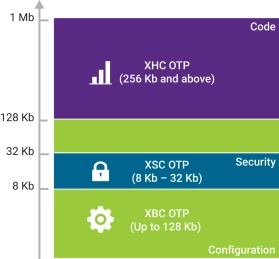

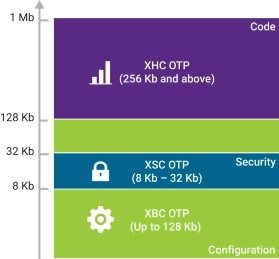

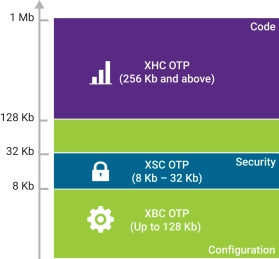

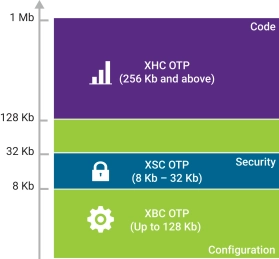

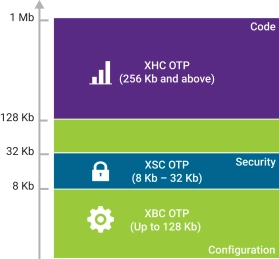

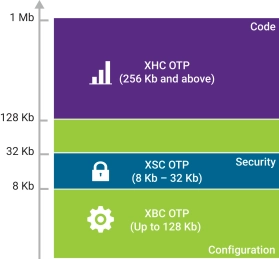

NVM OTP XBC TSMC N7 1.8V

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

NVM OTP XBC TSMC N6 1.8V

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

NVM OTP XBC TSMC N5A 1.2V Automotive Grade 1 with Functional Safety

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

NVM OTP XBC TSMC N5 1.2V

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

NVM OTP XBC TSMC N4P 1.2V

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

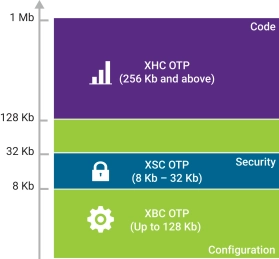

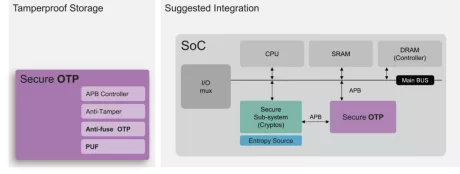

Secure OTP

- Up to 128kb mass production OTP with built-in instant hardware encryption (customization available)

- Comprehensive anti-tamper designs in physical and RTL

- APB control interface with secure/non-secure access privilege

- Four 256-bit hardware PUF fingerprints for scrambling drop-in-use Secure OTP Storage

-

OTP

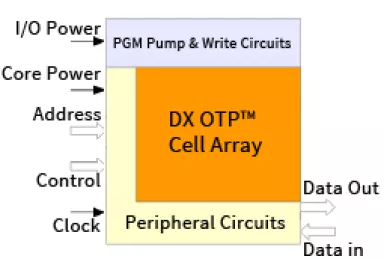

- Bit Cell Structure : 0.5 Transistor based

- Bit Cell Size : 7.5F2

- Bit Cell Process : Standard CMOS Logic Process plus one extra mask

- On-chip Capacity : Up to 256Mb beyond 4Mb Scalable to 20 nm node and below