OTP IP

Welcome to the ultimate OTP IP hub! Explore our vast directory of OTP IP

All offers in

OTP IP

Filter

Compare

1,083

OTP IP

from

7

vendors

(1

-

10)

-

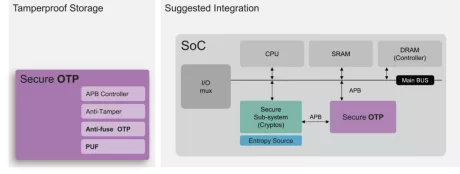

Secure OTP

- Up to 128kb mass production OTP with built-in instant hardware encryption (customization available)

- Comprehensive anti-tamper designs in physical and RTL

- APB control interface with secure/non-secure access privilege

- Four 256-bit hardware PUF fingerprints for scrambling drop-in-use Secure OTP Storage

-

OTP

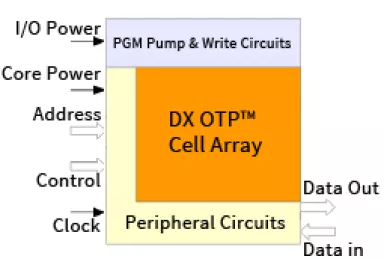

- Bit Cell Structure : 0.5 Transistor based

- Bit Cell Size : 7.5F2

- Bit Cell Process : Standard CMOS Logic Process plus one extra mask

- On-chip Capacity : Up to 256Mb beyond 4Mb Scalable to 20 nm node and below

-

64x1 Bits OTP (One-Time Programmable) IP, TSMC 0.18um SiGe BiCMOS 1.8V/3.3V General Purpose Process

- Fully compatible with TSMC 0.18um SiGe BiCMOS 1.8V/3.3V General Purpose process

- Wide operating voltage range:

- – Read voltage: 1.8 V ± 10% VDD and VDDP

- – Program Voltage: 2.7-3.63 V VDDP and 1.8 V ± 10% VDD

-

8Kx16 Bits OTP (One-Time Programmable) IP, DB HiTek AN180 1.8V / 5V Process

- Fully compatible with DB HiTek AN180 1.8V(w/ option-1) / 5V(Baseline) Process

- Program voltage: 3.75 V ± 5% VDDP, and 1.5–1.98 V VDD, 1 bit at a time

- Read voltage: 1.5–5.5 V VDDP and 1.5–1.98 V VDD, 16 bits at a time

- Access time: 10-us program time per bit. 200-ns (5 MHz) read cycle or 113-ns (8.8 MHz) read cycle with 75% duty cycle (TCKH = 85 ns) and SAP = 0

-

8Kx8 Bits OTP (One-Time Programmable) IP, MXIC 0.18um 1.8V/5V Logic/BCD Process

- Fully compatible with MXIC 0.18um 1.8V/5V Logic/BCD process

- Low voltage: 1.8 V ± 10% read and 3.9 V ± 0.1 V program

- High speed: 10-µs program time per bit, and 50-ns cycle time for read 8 bits

- Asynchronous input and latched output

-

1Kx1 Bits OTP (One-Time Programmable) IP, MXIC 0.18um 1.8V/5V CMOS Process

- Fully compatible with MXIC 0.18um 1.8V/5V CMOS process

- Wide operating voltage range:

- – Read voltage: 2.5-5.5V VDD and VDDP

- – Program Voltage: 5V+/-10% VDDP and 2.5-5.5V VDD

-

32x1 Bits OTP (One-Time Programmable) IP, MXIC 0.18um 1.8V/5V Logic Process

- Fully compatible with MXIC 0.18um 1.8V/5V logic process

- Wide operating voltage range:

- – Read voltage: 2.5-5.5V VDD and VDDP

- – Program Voltage: 5V+/-10% VDDP and 2.5-5.5V VDD

-

512x1 Bits OTP (One-Time Programmable) IP, MXIC 0.18um 1.8V/5V CMOS 18B Process

- Fully compatible with MXIC 0.18um 1.8V/5V CMOS 18B process

- Wide operating voltage range:

- – Read voltage: 2.5-5.5V VDD and VDDP

- – Program Voltage: 5V+/-10% VDDP and 2.5-5.5V VDD

-

16x8 Bits OTP (One-Time Programmable) IP, VIS 150nm 1.8V BCD Process

- Fully compatible with standard 0.15um BCD process

- Low voltage: 1.8V+/-10% core voltage and 3.7V+/-5% program voltage

- High speed: 10µs program time per bit and 300ns read cycle time, 8-bit at a time

- Asynchronous address and control input and latched output. CMOS levels I/Os

-

64x8 Bits OTP (One-Time Programmable) IP, Nexchip 0.15um 3.3V Logic Processes

- Fully compatible with Nexchip 0. 15um 3.3V logic processes

- Wide operating voltage range:

- – Read voltage: 1.62–3.63 V VDD and VDDP

- – Program Voltage: 3.45 V ± 5% VDDP and 1.62–3.63 V VDD