SATA PHY IP

Welcome to the ultimate SATA PHY IP hub! Explore our vast directory of SATA PHY IP

All offers in

SATA PHY IP

Filter

Compare

28

SATA PHY IP

from

9

vendors

(1

-

10)

-

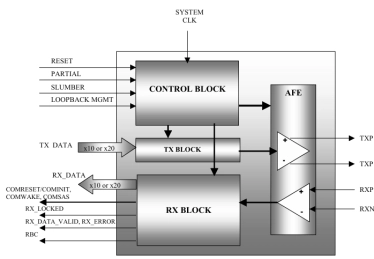

Serial ATA (SATA) PHY Transceiver IP

- SMS6000 is a fully integrated CMOS transceiver that handles the low level Serial ATA protocol and signaling.

- It contains all necessary Clock synthesis, Clock Recovery, Serializer, Deserializer, Comma detect for 8B/10B encoded data and Frame alignment functionalities.

-

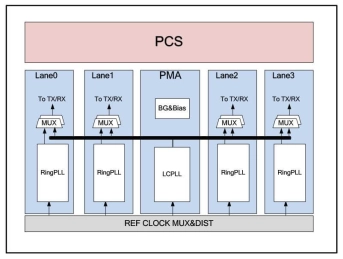

SATA/SAS 3.0 transceiver IP with PMA and PCS layer

- Highly customizable PMA configuration (controlled by PCS), X4 per Quad

- Support SATA data rate 1.5/3/6Gbps

- Support SAS data rate 1.5/3/6/12Gbps

- Digitally-control-impedance termination resistors

-

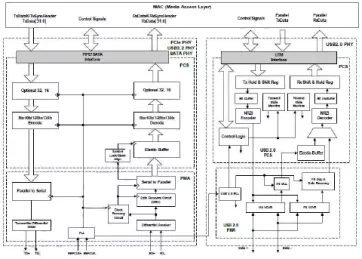

USB 3.2/ PCIe 3.1/ SATA 3.2 Combo PHY IP, Silicon Proven in UMC 28HPC

- Compliant with PCIe 3.1 Base Specification

- Compliant with Universal Serial Bus 3.2 Specification

- Compliant with Universal Serial Bus 2.0 Specification

- Compliant with UTMI 1.05 Specification

-

SATA 6G PHY in GF (40nm, 28nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

SATA 6G PHY in UMC (40nm, 28nm, 22nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

SATA 6G PHY in TSMC (40nm, 28nm, 16nm, 12nm, N7)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

SATA 6G PHY in SMIC (40nm, 28nm)

- Compliant with SATA/eSATA v3.3, AHCI v1.3 and SATA PIPE v4.3 specifications

- AMBA 2.0 AHB and AMBA 3 AXI subsystem interfaces

- AMBA 4 AXI and ACE-Lite bus interfaces

- Memory data protection and memory address parity protection

-

USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 28HPC+

- Compatible with PCIe/USB3/SATA base Specification

- Fully compatible with PIPE3.1 interface specification

- Data rate configurable to 1.5G/2.5G/3G/5G/6G for different application

- Support 16-bit or 32-bit parallel interface when encode/decode enabled

-

USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 22ULP

- Compatible with PCIe/USB3/SATA base Specification

- Fully compatible with PIPE3.1 interface specification

- Data rate configurable to 1.5G/2.5G/3G/5G/6G for different application

- Support 16-bit or 32-bit parallel interface when encode/decode enabled

-

SATA 6G PHY

- ? 6-Gbps transmission rate through standard SATA cable

- ? Spread-spectrum clock (SSC) generation and absorption

- ? Programmable down-spread (+4,980 ppm through -4,980 ppm)

- ? Fully clock-forwarded transceiver interface, configurable using soft PMA layer above hard macro PHY