MIPI DSI IP

As part of the MIPI (Mobile Industry Processor Interface) standard, MIPI DSI IP supports high-definition video and graphics transmission, making it ideal for smartphones, tablets, automotive displays, and wearables. With its ability to deliver high-quality image output while minimizing power consumption, MIPI DSI IP plays a vital role in enhancing the display performance of modern devices.

All offers in

MIPI DSI IP

Filter

Compare

45

MIPI DSI IP

from

17

vendors

(1

-

10)

-

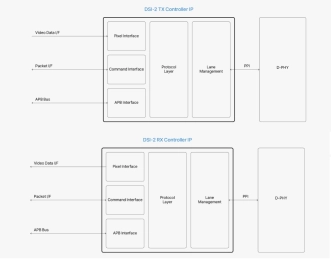

DSI-2 TX/RX Controller

- DSI-2 TX/RX IP supports both transmit and receive functions in line with the DSI-2 v1.1 and D-PHY v2.0 standards.

- Designed for modern SoCs integrating display functionality, it supports high-speed and low-power modes, lane configurability, and robust link features—making it ideal for advanced embedded display applications.

-

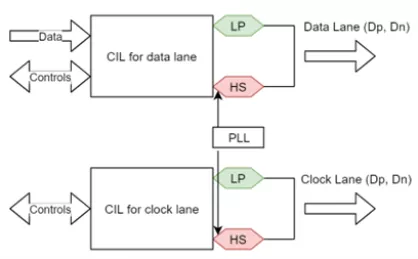

MIPI D-PHY TX PHY and DSI controller

- Scalability and Flexibility: Supports multiple data lanes for higher aggregate bandwidth, any of the multiple lanes can be configured into Clock Lane

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

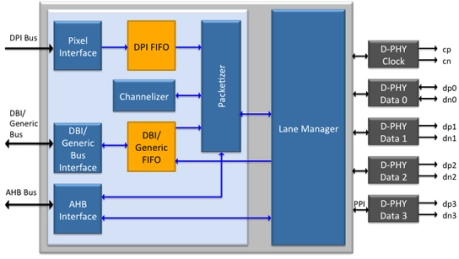

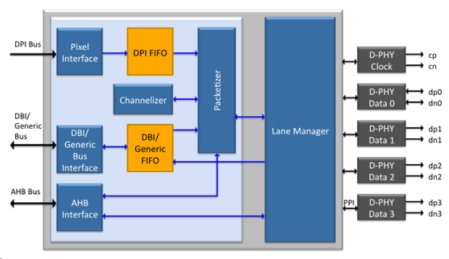

MIPI DSI-2 Transmitter Controller IP Core

- The MIPI Display Serial Interface (DSI-2) Transmitter (host processor interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

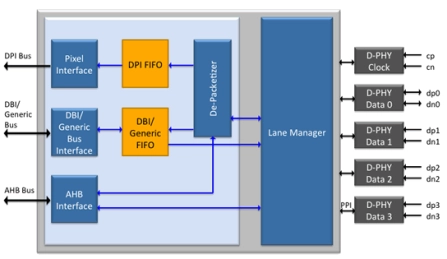

MIPI DSI-2 Receiver IP Controller Core

- The MIPI Display Serial Interface (DSI-2) Receiver (display panel interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

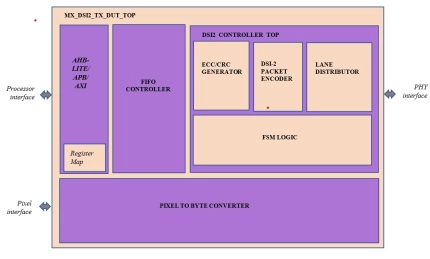

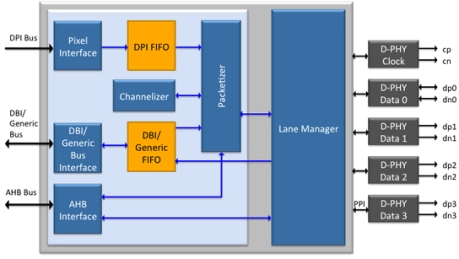

DSI v1.3 Transmit IP Core

- The DSI Tx Controller IP is designed to provide MIPI DSI 1.3 – compliant high-speed serial connectivity for the host (mobile application processor) using 1 to 4 D-PHYs depending on bandwidth needs.

-

DSI Receiver Controller

- The DSI v1.3 Receiver Controller IP is designed to provide MIPI DSI 1.3 compliant high-speed serial connectivity for device (mobile display modules) with Type 1 to 4 architectures.

- Serial connectivity to the mobile applications processor’s DSI host is implemented using 1 to 4 D-PHY’s (also available from Arasan), depending on display bandwidth needs.

-

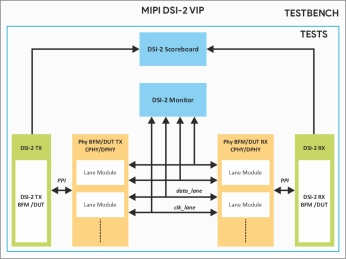

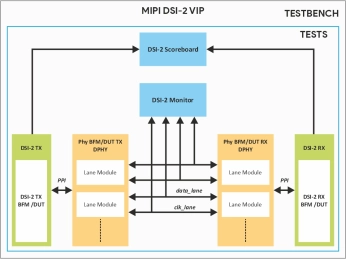

MIPI DSI v2.2 Verification IP

- Compliant to MIPI DSI Specification version 2.2 and MIPI C-PHY Specification version 2.1 with PPI interface.

- Support all Calibration Format & operations

- C-PHY supports MFAA and SFAA for DSI TX and RX respectively for Data Lane Module in command mode.

- C-PHY supports MFAN and SFAN for DSI TX and RX respectively for data Lane Module in video mode.

-

MIPI DSI v1.3.2 Verification IP

- Compliant to MIPI DSI Specification version 1.3.2 and MIPI D-PHY Specification version 1.2 with PPI interface.

- Support all Calibration Formats & operations

- D-PHY supports MFAA and SFAA for DSI TX and RX respectively for Data Lane Module in command mode.

- D-PHY supports MFAN and SFAN for DSI TX and RX respectively for Data Lane Module in video mode.

-

MIPI DSI2

- Fully MIPI DSI-2/DSI standard compliant

- 64 and 32-bit core widths

- Host (Tx) and Peripheral (Rx) versions

- Supports 1-4, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

-

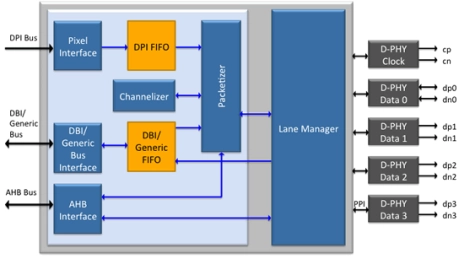

MIPI DSI DisplayTransmitter IP

- MIPI DSI Transmitter IP is designed to transmit the data to the host processor

- The MIPI DSI-2 provides the mobile industry a standard, robust, scalable, low-power, high-speed, cost-effective interface that supports a wide range of imaging solutions for mobile devices