Ultra Low Latency 10G TCP Endpoint

The TCP Endpoint implements a full, reliable streaming network stack in FPGA logic.

Overview

The TCP Endpoint implements a full, reliable streaming network stack in FPGA logic. It allows applications in logic to be directly connected to Internet Protocol (IP) interfaces by opening, maintaining, and closing TCP Connections via Ethernet to other hardware or software endpoints.

The mature, reliable, and network-tested TCP Endpoint delivers high performance with ultra-low latency. It runs at the full 10 Gigabit Ethernet line rate with a clock speed synchronous with a MAC and application processing logic. It supports full duplex rates of 20 Gbps per instance. The implementation is portable between Intel and Xilinx FPGA devices and has been deployed on multiple platforms.

The TCP Endpoint is available as a pre-integrated component in low latency applications or as a standalone IP. It has been deployed in customer applications including pre-trade risk-checks, complete tick-to-trade applications, and other flow processing applications. Algo-Logic provides in-house engineering support to ensure complete solution delivery with support for end-system and application-level fastest deployments.

Key features

- Full TCP/IP stack in FPGA logic

- Layer 1: IEEE802.3

- Layer 2: IEEE802.3, ARP

- Layer 3: IPv4 and ICMP

- Layer 4: TCP

- Ultra-low latency

- RTL design for optimal performance

- Optional cut-through for receive (RX) and transmit (TX) data.

- Parameters

- Retransmission timeouts

- Size of shared on-chip retransmission buffer

- Option for fast retransmission

- Limits on retransmissions

- TX Rewind

- Streaming Interfaces with in-order data

- AXI-4

- Avalon

- High network bandwidth

- Multiple instances allow for more than 200 Gbps to a single FPGA device

- Control registers

- Configurable over network or PCIe

- TCP option support: MSS, window scaling, timestamps

- Robust flow control and error control

- Advanced statistics for monitoring TCP sessions in real-time

- Exchange-certified in trading systems

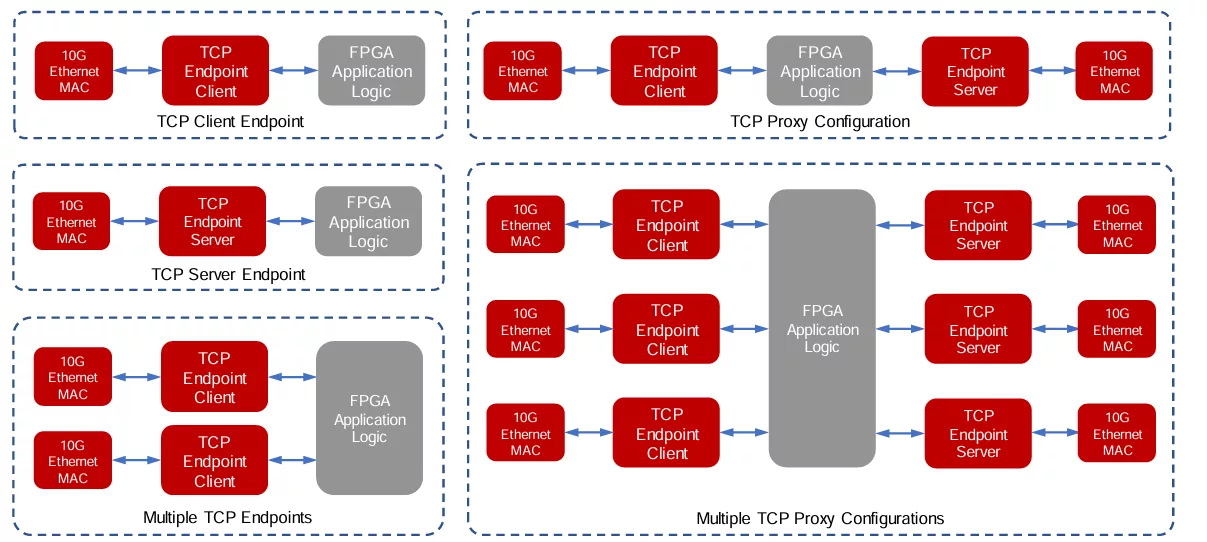

Block Diagram

Applications

- High frequency trading

- Tick-to-Trade systems

- Pre-trade risk checks

- Reliable, filtered feed redistribution

- Trading/arbitrage opportunity discovery

- Proprietary/algorithmic trading strategies

- Financial surveillance systems

- Network attached storage

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Ultra Low Latency 10G TCP Endpoint?

Ultra Low Latency 10G TCP Endpoint is a Ethernet IP core from Algo-Logic Systems listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.