I²S IP Cores

I²S (Inter-IC Sound) IP Cores provide a robust and standardized digital audio interface for transmitting and receiving PCM audio data between integrated circuits in SoC and FPGA-based systems. Designed to implement the I²S protocol as defined by Philips, these IP cores enable seamless communication between audio ADCs, DACs, DSPs, and audio codecs.

Explore our vast directory of I²S IP Cores below.

All offers in

I²S IP Cores

Filter

Compare

20

I²S IP Cores

from

15

vendors

(1

-

10)

-

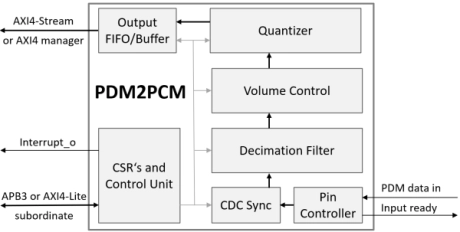

PDM Receiver/PDM-to-PCM Converter

- This PDM2PCM is a configurable audio interface core that converts a mono or stereo Pulse Density Modulation (PDM) stream into standard Pulse Code Modulation (PCM) format.

- PCM output widths are programmable from 2 to 32 bits, and all standard audio sampling rates are achievable via an adjustable Oversampling Ratio (OSR) from 32x to 256x.

-

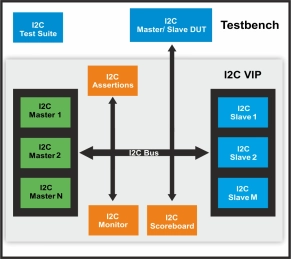

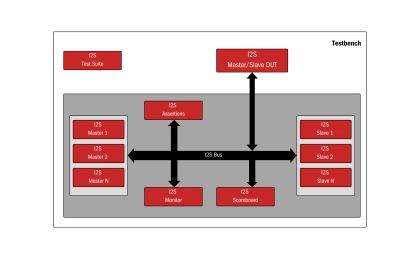

I2C/I2S/LPC Verification IP

- Fully compliant with Rev. 6 of the I2C-Bus Specification and backward compatible upto 2.1 version

- Full I2C Master and Slave functionality

- Master Transmitter/Master Receiver

- Slave Transmitter/Slave Receiver

- Master Transmitter/Master Receiver

- Slave Transmitter/Slave Receiver

-

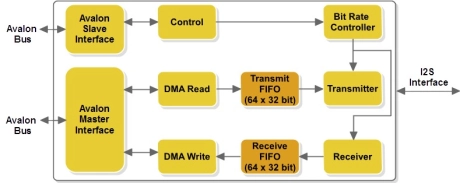

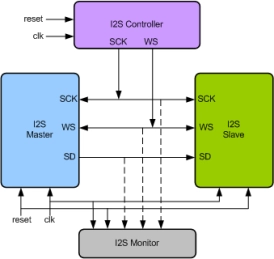

I2S Controller

- I²S Controller is designed to transfer audio data to and from Audio codec.

- It can be configured as both Master and Slave mode using software.

- The I²S IP is Phillips Inter IC Sound (I²S) specification compliant core for Altera devices.

-

I2S Verification IP

- Complies with Philips I2S Specification June 5, 1996

- Full I2S Transmitter, Receiver and Controller functionality

- Supports up to 32 channels in transmit path

- Supports up to 32 channels in receive path

-

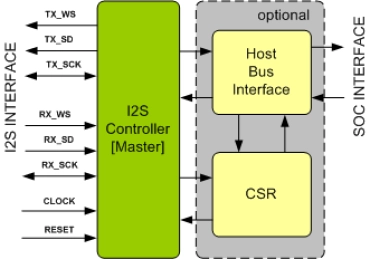

I2S Controller IIP

- Compliant with the Philips I2S Bus Specification

- Master mode as Controller

- Slave mode as transmitter and receiver

- Bidirectional operation through two unidirectional serial data lines

-

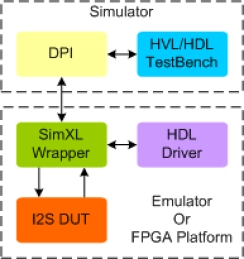

I2S Synthesizable Transactor

- Supports Philips I2S Bus Specification June 5, 1996

- Full I2S Transmitter, Receiver and Controller functionality

- Supports up to 32 channels in transmit path

- Supports up to 32 channels in receive path

-

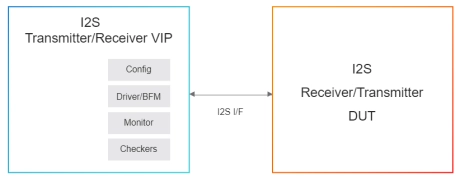

Simulation VIP for I2S

- Configurability

- Fully configurable VIP configuration: Manager/Subordinate, Transmitter/Receiver, Active/Passive

- Word Length Programmability

- Supports 8, 12, 16, 20, 24, 32, and user-defined

-

I2S - Ensures proper audio data transmission, synchronization, and integrity

- I2S (Inter-IC Sound) is a serial bus interface used for connecting digital audio devices. As a Verification IP (VIP), it ensures proper data transmission, signal integrity, timing, and protocol compliance in audio communication systems.

- This VIP verifies key elements such as word length, frame synchronization, clock behavior, and error handling, making it essential for testing I2S communication in a range of applications, including consumer electronics, automotive, and medical devices

-

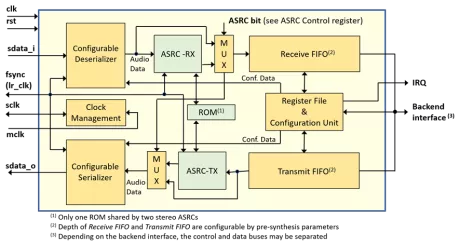

I2S/TDM Serial Audio Interface with Asynchronous Sample Rate Conversion

- The IPB-I2S-TDM-ASRC combines an I2S/TDM configurable serial audio interface with two embedded stereo Asynchronous Sample Rate Converters (ASRCs).

- The ASRCs can provide very high quality in terms of harmonic distortion and noise, tolerance and rejection of input jitter.

-

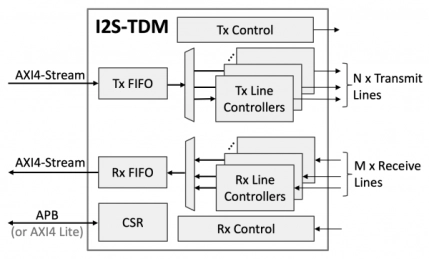

I2S/TDM Multichannel Audio Transceiver

- The I2S-TDM IP core is a highly configurable, full-duplex, multichannel serial audio transceiver.

- The transceiver can act as a controller (master) or a target (slave) for Inter-IC Sound (I2S) and Time-Division Multiplexed (TDM) audio interfaces, exchanging mul-ti-channel audio samples over a configurable number of serial lines (pins).