Frac-N PLL IP for UMC

Welcome to the ultimate

Frac-N PLL IP

for

UMC

hub! Explore our vast directory of

Frac-N PLL IP

for

UMC

All offers in

Frac-N PLL IP

for

UMC

Filter

Compare

8

Frac-N PLL IP

for

UMC

from

3

vendors

(1

-

8)

-

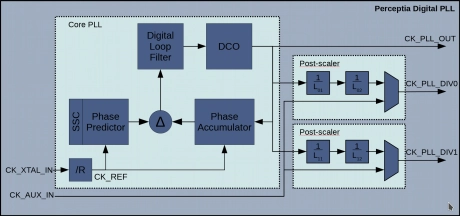

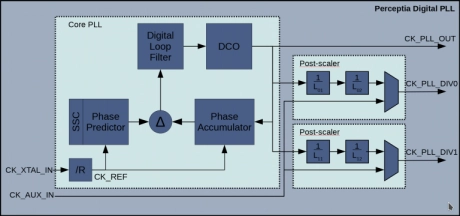

All Digital Fractional-N PLL for Performance Computing in UMC 40LP

- Fractional multiplication with frequency up to 4GHz

- Low jitter (< 10ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 5mW)

-

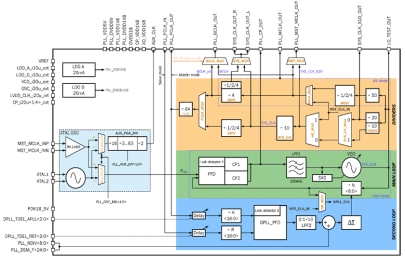

2.26GHz/2.46GHz Fractional-N LC Phase-Locked Loop with oscillator

- 180XFAB_PLL_01 uses 2.25792GHz/2.4576GHz Phase locked loop frequency synthesizer for clock generation.

- It consists of the following main sub-blocks: reference oscillator; main PLL loop: Fractional-N PLL and VCO blocks; secondary digital PLL loop: synchronization subsystem; dividers block: clock generation/delivery subsystem; voltage stabilizers.

- High frequency synthesis is needed for both phase noise performance and ultra-fine frequency tuning step.

-

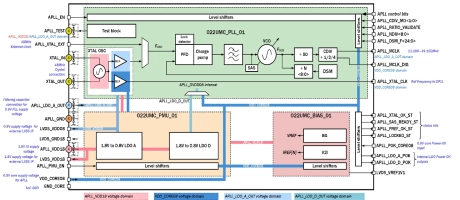

10MHz to 50MHz fractional-N PLL synthesizer

- UMC 22nm ULP technology

- 1.8V IO power supply

- Double 0.8/1.0V Core power supply

- Embedded low noise bias

-

All Digital Fractional-N RF Frequency Synthesizer PLL in UMC 40LP

- Fractional Multiplication with frequencies up to 8GHz

- Extremely low jitter (< 300fs RMS)

- Small size (< 0.05 sq mm)

- Low Power (< 15mW)

-

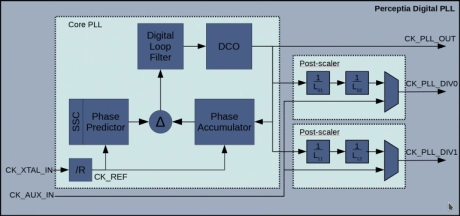

General Purpose All Digital Fractional-N PLL in UMC 40LP

- Low jitter (< 18ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 3.5mW)

- Support for multi-PLL systems

-

General Purpose All Digital Fractional-N PLL in TSMC N6/N7

- Low jitter (< 18ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 3.5mW)

- Support for multi-PLL systems

-

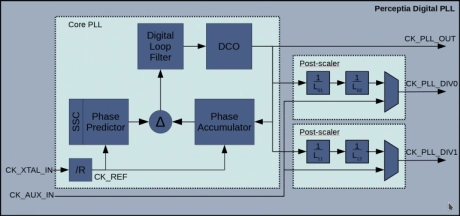

Aeonic Generate Clock Generation Module [PLL], 8x smaller than fractional analog solutions

- Process portable

- Proven (65nm to 3nm)

- Full SCAN testable

- Core voltage supply