LCD Controller IP for TSMC

Welcome to the ultimate

LCD Controller IP

for

TSMC

hub! Explore our vast directory of

LCD Controller IP

for

TSMC

All offers in

LCD Controller IP

for

TSMC

Filter

Compare

6

LCD Controller IP

for

TSMC

from

3

vendors

(1

-

6)

-

Customizable Display Controller IP

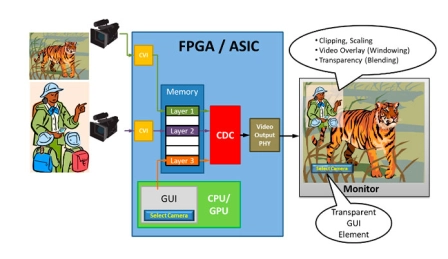

- CDC is a fully Customizable Display Controller IP supporting up to 16k resolutions (4096x4096 pixel) on a MIPI-DPI compliant parallel video output.

- Several features can be configured at synthesis time and programmed at run time.

- The display controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

Customizable Video Input controller

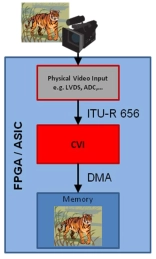

- CVI is a fully Customizable Video Input controller IP core.

- The video input controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

Display Controller – 4K Digital Cinema LCD Panels (AXI4/AXI Bus)

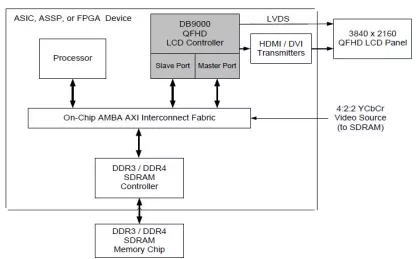

- The DB9000AXI-DCI LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to a 4K and 2K Digital Cinema Initiative (DCI) High Definition TFT LCD panel

- The video image in frame buffer memory can be 8/10/12-bit YCrCb or RGB, with a Color Space Convert to match the source video to the TFT LCD panel requirements

-

Display Controller - LCD / OLED Panels (AHB Bus)

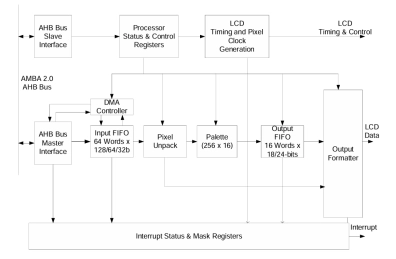

- The DB9000AHB TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the AMBA 2.0 AHB Bus to a TFT LCD panel.

- In an FPGA, ASIC, or ASSP device, the microprocessor is an ARM processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

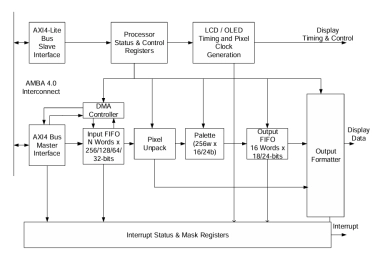

Display Controller - LCD / OLED Panels (AXI4 Bus)

- Advanced display processing, such as Multi-layer Overlay Windows with composition features such as Alpha Blending, Color Space Conversion, 4:2:0 and 4:2:2 YCrCb color with Re sampling & conversion to RGB, Frame Buffer Compression and Hardware Cursor

-

Dual FPD-link, 30-Bits Color LVDS Receiver, 170Mhz (SVGA/FHD@120Hz) LVDS de-serializer 10:70 channel decompression with automatic de-skew

- Layout structure based on 0.13um Logic 1P6M, 1P7M, or 1P8M Salicide 1.2V/3.3V process.

- 1.2V/3.3V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3- 1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 11.9Gbps bandwidth (40 to 170Mhz pixel clock) per pixel channel (Full HD @ 120Hz)