Other for TSMC

Welcome to the ultimate

Other

for

TSMC

hub! Explore our vast directory of

Other

for

TSMC

All offers in

Other

for

TSMC

Filter

Compare

4

Other

for

TSMC

from

2

vendors

(1

-

4)

-

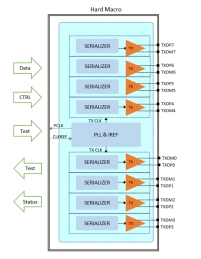

SLVS-EC TX PHY - 10GBPS 8-Lane - TSMC 12FFC

- SLVS-EC ver.3.0 compliant

- Data Rate: Up to 10Gbps / lane

- Number of data lane: 8

- Support input clock: 24MHz, 54MHz, 37.125MHz, 72MHz, 74.25MHz

-

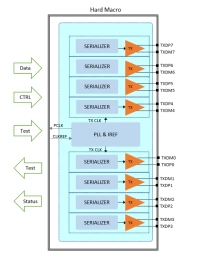

Camera Receiver - 10.0Gbps 8-Lane - TSMC 12FFC

- The CL12812M8RIP10000 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processor) and DSP.

- The CL12812M8RIP10000 is designed to support data rate in excess of maximum 10Gbps utilizing SLVS-EC ver.3.0 interface specification.

-

Camera Receiver - 5.0Gbps 8-Lane - TSMC 12FFC, 6FFC

- The CL12812M8RIP5000 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processor) and DSP.

- The CL12812M8RIP5000 is designed to support data rate in excess of maximum 5Gbps utilizing SLVS-EC ver.3.0 BG3 interface specification

-

XAUI PHY

- ? 3.125-Gbps transmissions rate

- ? Supports x4 configuration

- ? Integrated regulator to support either 3.3-V or 2.5-V I/O power supply

- ? Excellent performance margin and receiver sensitivity