Frac-N PLL IP for TSMC

Welcome to the ultimate

Frac-N PLL IP

for

TSMC

hub! Explore our vast directory of

Frac-N PLL IP

for

TSMC

All offers in

Frac-N PLL IP

for

TSMC

Filter

Compare

23

Frac-N PLL IP

for

TSMC

from

7

vendors

(1

-

10)

-

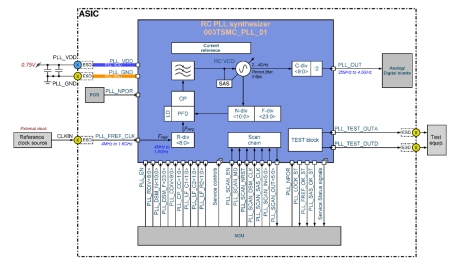

25MHz to 4.0GHz Fractional-N RC PLL Synthesizer on TSMC 3nm N3P

- Fractional-N Phase locked loop frequency synthesizer is intended for ASIC clock generation.

- The Fractional-N PLL loop with 2GHz-4GHz VCO has high phase noise performance and ultra-fine frequency tuning step.

- VCO Sub-band auto select (SAS) system allows to find automatically appropriate sub-band for VCO on locked PLL.

-

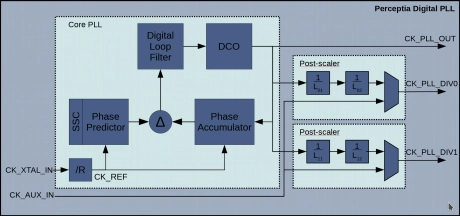

All Digital Fractional-N RF Frequency Synthesizer PLL in TSMC N6/N7

- Fractional Multiplication with frequencies up to 8GHz

- Extremely low jitter (sub 300fs RMS)

- Small size (< 0.05 sq mm)

- Low Power (< 7mW)

-

All Digital Fractional-N PLL for Performance Computing in TSMC N6/N7

- Fractional multiplication with frequency up to 4GHz

- Low jitter (< 10ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 5mW)

- Support for multi-PLL systems

-

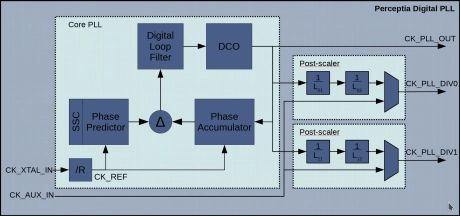

Low Power All Digital Fractional-N PLL in TSMC N6/N7

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

Low Power All Digital Fractional-N PLL in Samsung 8LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

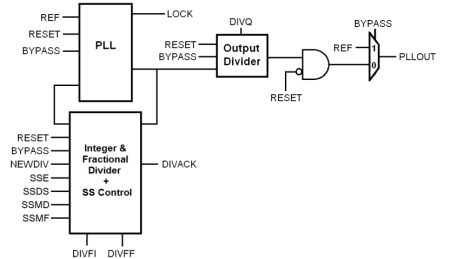

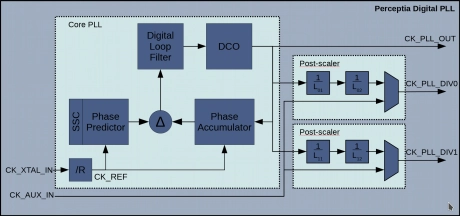

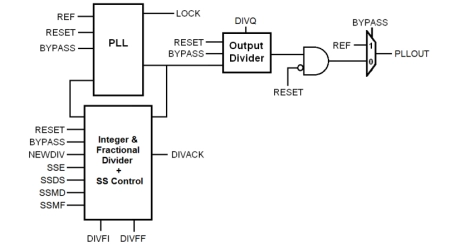

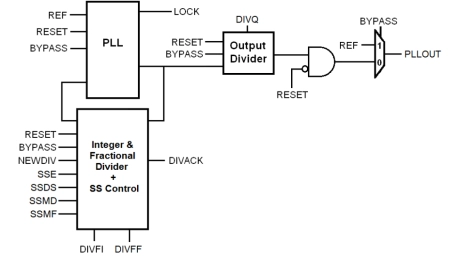

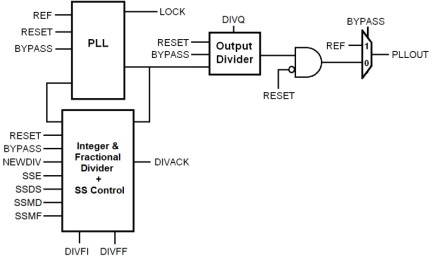

Low Power FracN/SSCG PLL on TSMC CLN6FF

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution

- Fully integrated 32-bit datapath (8-bit integer plus 24-bit fractional)

-

FracN/SSCG PLL on TSMC CLN5

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution

- Fully integrated 32-bit datapath (8-bit integer plus 24-bit fractional)

-

Core Powered FracN/SSCG PLL on TSMC CLN7FF

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution

- Fully integrated 32-bit datapath (8-bit integer plus 24-bit fractional)

-

Core Powered FracN/SSCG PLL on TSMC CLN5A

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Entirely core voltage powered, needs no analog supply voltage

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution

-

Core Powered FracN/SSCG PLL on TSMC CLN5

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Entirely core voltage powered, needs no analog supply voltage

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution