Clock Generator PLL IP for SMIC

Welcome to the ultimate

Clock Generator PLL IP

for

SMIC

hub! Explore our vast directory of

Clock Generator PLL IP

for

SMIC

All offers in

Clock Generator PLL IP

for

SMIC

Filter

Compare

3

Clock Generator PLL IP

for

SMIC

from

3

vendors

(1

-

3)

-

Phase-locked loop system 2.8 to 3.3 GHz

- SMIC CMOS 0.18 um

- Wide frequency range (2.8…3.3 GHz)

- Built-in switched capacitors sections for VCO frequency adjustment

- Low noise figure

-

-

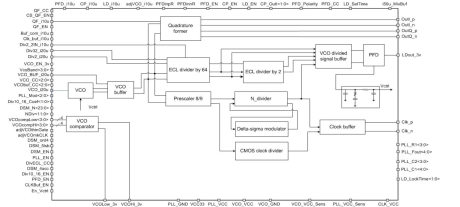

SMIC 28nm High-K 1.8V/0.9V PLL

- Process:SMIC 28nm High-k 1.8V/0.9V process

- Supply voltage: 1.62V<=AVDD<=1.98V,0.81V<=DVDD(AVDD2)<=0.99

- Mos device type: nfet, pfet, egnfet, egpfet, mom_2t

- Operating current: AVDD<1.2mA(1GHz) AVDD<4.8mA(3.2GHz)