IP for LFoundry

-

I2C Controller IP – Master, Parameterized FIFO, AXI Bus

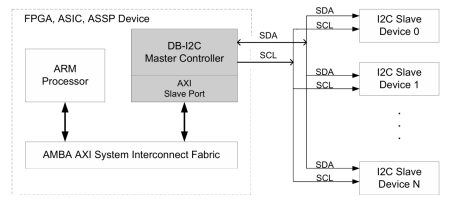

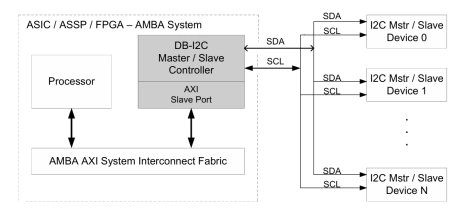

- The DB-I2C-M-AXI Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high performance microprocessor via the AMBA 2.0 AXI System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-M-AXI is a Master I2C Controller that controls the Transmit or Receive of data to or from slave I2C devices. Figure 1 depicts the system view of the DB-I2C-M AXI Controller IP Core embedded within an integrated circuit device.

-

I2C Controller IP- Master / Slave, Parameterized FIFO, AHB Bus

-

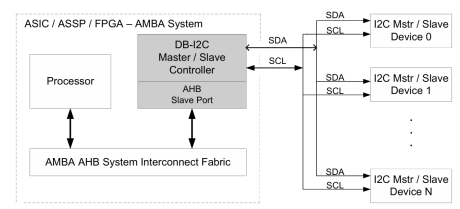

The DB-I2C-MS-AHB Controller IP Core interfaces a microprocessor via the AMBA AHB Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

The DB-I2C-MS-AHB is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

-

I2C Controller IP- Master / Slave, Parameterized FIFO, APB Bus

-

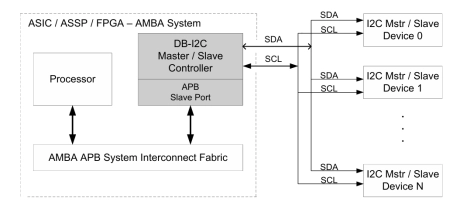

The Digital Blocks DB-I2C-MS-APB Controller IP Core interfaces a microprocessor via the AMBA APB Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

The DB-I2C-MS-APB is a Master/Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

-

I2C Controller IP- Master / Slave, Parameterized FIFO, AXI Bus

- The DB-I2C-MS-AXI Controller IP Core interfaces a microprocessor via the AMBA AXI Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-MS-AXI is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

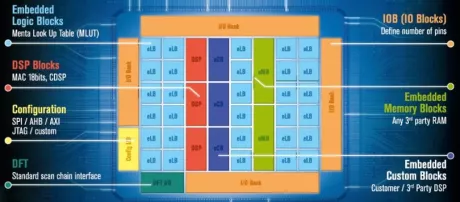

eFPGA Soft IP

- These eFPGA IP cores offer designers the flexibility to tailor resources to their application requirements, available as either Soft RTL or Hard GDSII IP.

- Our standard-cell-based approach facilitates rapid porting to new process geometries or variants, including industrial and rad-hard grade versions.

-

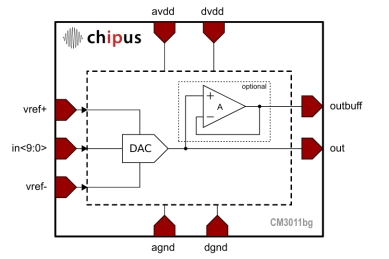

General Purpose 10-bit DAC - 10 bits, 2MSPS, buffered output option - LFoundry 0.15µm LF150 CMOS

- This macro-cell is a general purpose, 10-bit, 2MSPS, resistive Digital-to-Analog Converter (DAC) core designed for LFoundry 0.15μm LF150 CMOS technology STD (Standard) and LP (Low Power) process.

- The circuit has internal optional buffer to drive directly light loads and is optimized for low power consumption.

-

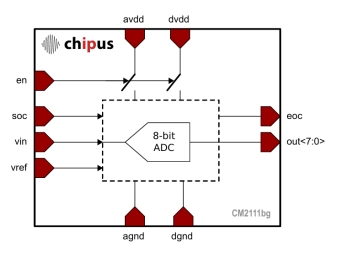

Ultra Low Power 8-bit ADC - Ultra Low Voltage (1V), Ultra Low Power (850nA) - LFoundry 0.15µm

- This macro-cell is a general purpose, ultra low power, 8-bit, time-based Analog-to-Digital Converter (ADC) core designed for LFoundry 0.15μm LF150 CMOS technology STD (Standard) and LP (Low Power) process.

- The circuit is ideal for general purpose/auxiliary low frequency measurements (such as power supply voltage monitor) in applications in which ultra low power consumption is mandatory.

-

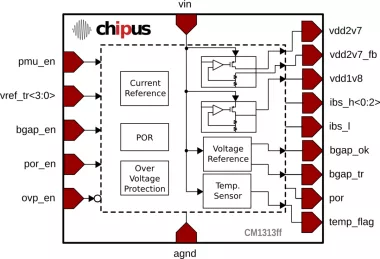

General Purpose PMU - Thermal shutdown and overvoltage protected - SilTerra 0.18 um

- This macro-cell is a Power Management Unit (PMU) core designed for Silterra 0.18µm C18GH5 CMOS technology in TO (thick oxide) and HP (thin oxide) process.

- The circuit has two linear voltage regulators (one of which has an external feedback connection), internal voltage and bias current generators, built-in poweron-reset (POR), thermal shutdown and overvoltage protection.

-

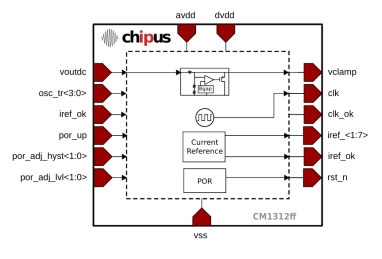

Ultra Low Power PMU - (2.18µW) - SilTerra 0.18 um

- This macro-cell is an ultra low consumption Power Management Unit (PMU) core designed for Silterra 0.18µm C18G CMOS technology TO (thick oxide) and HP (thin oxide) process.

- The circuit has a shunt regulator, internal voltage and bias current generators, built-in power-on-reset and oscillator.

-

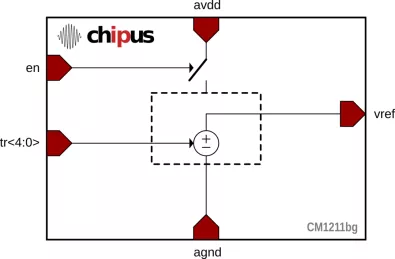

Bandgap Voltage Reference Low TC (13ppm/ °C), PSRR-42 dB @ 100kHz

- This macro-cell bandgap voltage reference generator core designed for SilTerra 0.18µm CL18GH5 CMOS technology.

- The core is ideal as a general purpose reference voltage in applications where low TC is required with quick response dynamic.