Datapath IP

Welcome to the ultimate Datapath IP hub! Explore our vast directory of Datapath IP

All offers in

Datapath IP

Filter

Compare

5

Datapath IP

from

2

vendors

(1

-

5)

-

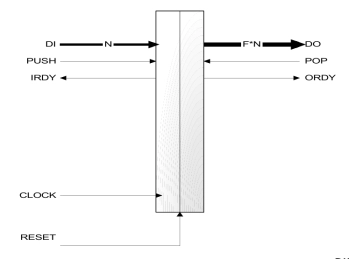

Stallable pipeline stage with width contraction

- The PIPE is a double register plus a small state machine that enables a fully synchronous stall-able pipeline to be built.

- A parameter defines the ratio of the input width to the output width.

- For example, if the input width is 32-bits and the Reduction Factor is 4 the the output width is 8-bits.

-

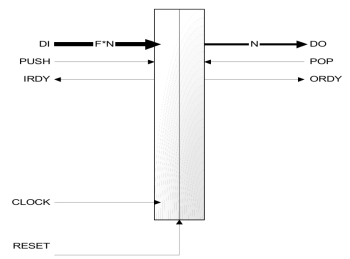

Stallable pipeline stage with width expansion

- The PIPE is a double register plus a small state machine that enables a fully synchronous stall-able pipeline to be built.

- A parameter defines the ratio of the input width to the output width.

- For example, if the input width is 8-bits and the Expansion Factor is 4 the the output width is 32-bits.

-

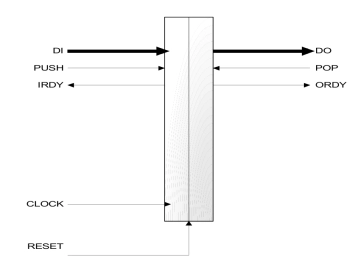

Stallable pipeline stage with protocol for multiway pipeline fork and join capability

- The PIPE is a double register plus a small state machine that enables a fully synchronous stall-able pipeline to be built.

- The interface is fully compatible with a Standard FIFO interface and they may be mixed and matched.

- A “Stall” may be generated by gating the POP and ORDY signals to arrest the normal flow of data down the pipeline and allows any given stage to take multiple cycles when necessary.

-

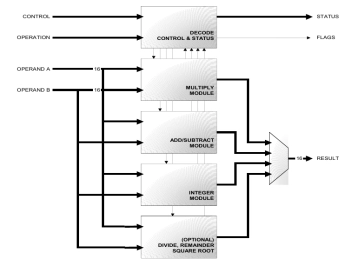

Half Precision IEEE-754R complete FPU for graphics processing

- The A2FH is a co-processor unit providing floating-point computation compliant with the ANSI/IEEE Std 754-2008, IEEE Standard for Binary Floating-Point Arithmetic (IEEE-754R Standard).

- It is designed to provide a powerful floating-point functionality for low-power, low frequency applications.