Arasan's Universal Flash Storage 2.1 (UFS 2.1) is a simple but high performance, serial interface primarily used in mobile systems, between host processing and nonvolatile eXecute-In-Place (XIP) or mass storage memory devices.

Mobile phones, UMPC, DSC, PMP are some of the typical applications for UFS Host Controller IP. Majority of these applications require mass storage and bootable storage memory with an option for an external card.

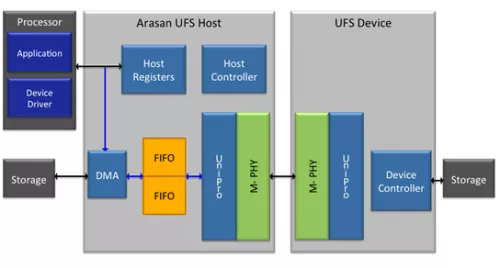

The IP incorporates the latest UFS Host Controller Interface (HCI) version 2.0. Arasan’s MIPI M-PHY® HS-G3 IP is available in GDSII format for a variety of process technologies and MIPI UniProSM version 1.6 link layer with support for multi-lane operation and the optional Unified Memory Architecture (UMA) implementation.

UFS 2.1 Host Controller compatible with M-PHY 3.1 and UniPro 1.6

Overview

Key Features

- JEDEC UFS 2.1 and UFS HCI 2.0 Compliant

- Supports high performance M-PHY v3.1 type-1

- 2 lanes @ 5.9 Gbps per lane

- UniPro v1.6 link layer

- Definable write-protect group size

- Boot mode operation

- Device enumeration and discovery

- Background operation

- Secure Erase and Trim operations enhance security

- Write-protect options include permanent and power-on protection

Benefits

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

Block Diagram

Video

UFS 2.1 Host Controller

UFS 2.1 Host Controller

Deliverables

- RTL Source code

- Synthesis scripts

- Test Environment

- Technical documents

Technical Specifications

Availability

Now

Related IPs

- UFS 2.1 Device Controller compatible with MIPI M-PHY 3.1 and UniPro 1.6

- UFS 3.1 Host Controller compatible with M-PHY 4.1 and UniPro 1.8

- MIPI UFS v2.1 Host Controller IP, Compatible with M-PHY and Unipro

- MIPI UFS v3.1 Host Controller IP, Compatible with M-PHY and Unipro

- UFS 4.0 Host Controller compatible with M-PHY 5.0 and UniPro 2.0

- SpaceWire link controller with SpaceWire RMAP support and AMBA host interface