Arasan Chip Systems is a leading SoC IP provider of a complete suite of JEDEC UFS compliant IP solutions, which consist of IP cores, verification IP, software stacks and drivers, hardware platforms for software development and compliance testing, and optional customization services.

Universal Flash Storage (UFS) is a JEDEC standard for high performance mobile storage devices suitable for next generation data storage. UFS is also adopted by MIPI as a data transfer standard designed for mobile systems. Most UFS applications require large storage capacity for data and boot code. Applications include mobile phones, tablets, DSC, PMP, MP3, and other applications requiring mass storage, boot storage, XiP or external cards.

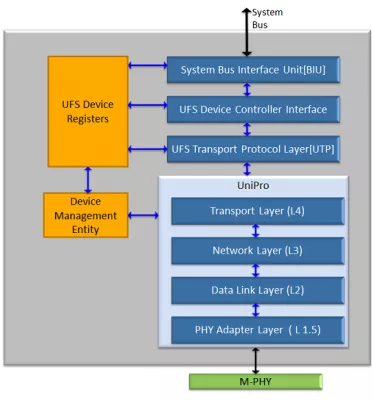

The UFS standard is a simple but high-performance serial interface that efficiently moves data between a host processor and mass storage devices. USF transfers follow the SCSI model, but with a subset of SCSI commands. The Arasan UFS IP family consists of UFS 2.1 Host controller IP, UFS 2.1 Device controller IP, and M-PHY3.1. Arasan’s UFS 2.1 digital controller IP has incorporated the MIPI UniPro version 1.6 link layer with support for multi-lane operation and the optional Unified Memory Architecture (UMA) implementation.

The UFS compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms. This leads to smaller footprint, greater interoperability between mobile IP, chips and devices from diverse sources, and lower power and EMI.

UFS 2.1 Device Controller compatible with MIPI M-PHY 3.1 and UniPro 1.6

Overview

Key Features

- Compliant with JESD220B UFS 2.1

- MIPI UniPro version 1.6

- Interface supported

- AXI

- Optional AHB, OCP

- High-performance M-PHY v3.0 type 1

- Core features

- 2 lanes @ 5.9 Gbps per lane

- Low power with multiple power operating modes

- Configurable Transmit and Receive FIFOs

- Error detection and reporting. Support Data and Task management

- Support for multiple commands and tasks

Benefits

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

Block Diagram

Deliverables

- RTL Source code

- Synthesis scripts

- Test Environment

- Technical documents

Technical Specifications

Maturity

Pre-silicon

Availability

Now

Related IPs

- UFS 2.1 Host Controller compatible with M-PHY 3.1 and UniPro 1.6

- MIPI UFS v3.1 Device Controller IP, Compatible with M-PHY and Unipro

- UFS 3.1 Host Controller compatible with M-PHY 4.1 and UniPro 1.8

- MIPI UFS v2.1 Host Controller IP, Compatible with M-PHY and Unipro

- MIPI Unipro v1.8 Controller IP, Compatible with M-PHY and UFS

- UFS 3.0 Host Controller compatible with M-PHY 4.0 and UniPro 1.8