Provider

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about UFS Controller IP core

As the system, software & IP complexity is increasing so is the demand of SystemC models & Virtual Platform for verification. To achieve it, the key requirements are that the models/platform should be developed fast, reusable & highly accurate. We are sharing the experience of our company 3D-IP Semiconductors Ltd. for the development of a generic Virtual Platform using TLM 2.0; reusable for any system model.

In the world of mobile and embedded electronics, storage is no longer just about capacity; it’s about how fast that data can move. As we transition into an era of on-device AI and 8K video, the standards we rely on—UFS, eMMC, and NAND—are evolving rapidly.

With the rapid development of modern mobile systems there is a great increase in the complexity involved in the IP and SOC designs and correspondingly the functional verification also becomes a challenge. To reduce time to market, IPs needed for the SOC must be developed in parallel to the top level design and should be verified in parallel. This requires strong methodology and infrastructure support which allows the SOC design team to be aligned on the requirements with IP teams. Methodology should also ensure that SOC design team gets the required data for the IP to proceed with the complexity of SOC design.

Eric Esteve

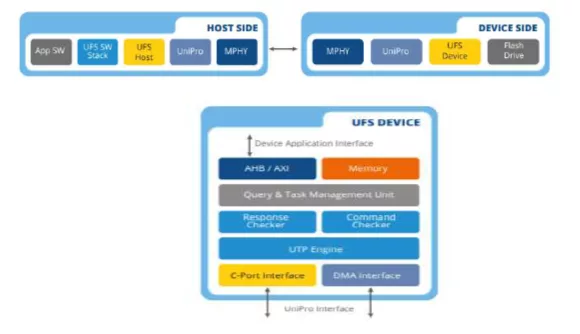

UniversalFlash Storage (UFS) was created for mobile applications and computer systems requiring high performance and low power consumption. These systems typically use embedded Flash based on the JEDEC standard eMMC. UFS was defined by JEDEC as the evolutionary replacement for eMMC offering significantly higher memory bandwidth. The standard builds on existing standards such as the SCSI command set, the MIPI Alliance M-PHY and UniPro as well as eMMC form factors to simplify adoption and development.

In today's world of increasingly intelligent devices, efficient and reliable storage is paramount. Embedded MultiMediaCard (eMMC) has emerged as a crucial component that acts as the internal solid-state non-volatile storage for a wide range of devices handling on-device AI processing. Think of it as a compact, high-performing internal drive built directly into your phone, smart camera, or other embedded systems. This blog explores what makes eMMC such a valuable solution, especially for AI applications: