NEMA®|dc is a powerful display controller which contains several smart tools and functionalities to compose multiple graphics and video layers by improving image quality and contributing significantly to the reduction of the SoC power consumption. NEMA®|dc supports powerful composition features, a wide range of display interfaces, and advanced proprietary frame-buffer compression technology.

The core is designed to lift the workload off the Graphics Processing Unit (GPU) or the host processor (CPU), in GPU-less systems, and minimize the memory bandwidth. Multiple layers can be clipped, positioned and composed on the final display by overlaying video, subtitles, graphics, cursor or application windows, with or without transparency.

TFT/LCD/MIPI Display Controller and Composition Engine

Overview

Key Features

- CORE FEATURES

- Programmable display resolutions up to 32Kx32K, including: VGA, XGA, HD, Full-HD, Quad Full-HD**, 4K**

- Multiple input graphics or video layers

- Powerful composition

- Alpha blending

- Programmable size, offset and format per layer

- Programmable stride/pitch enabling panning and clipping

- RGB to YUV(YCbCr) conversion

- Per layer palette

- Global or per layer Gamma correction

- Dithering for better results on 18-bit displays

- Fixed or programmable cursors (32 x 32)

- ** Please check system requirements

- DISPLAY INTERFACES

- MIPI DPI (Parallel RGB)

- MIPI DBI-Type B

- Parallel YUV

- 2, 3 and 4 bit serial RGB

- Programmable HSYNC, VSYNC, DE, pixel clock polarity

- 3 - 4 Wire SPI (MIPI DCS commands)

- Dual SPI, Quad SPI (DDR)

- Serial JDI display (SPI)

- CONFIGURATION OPTIONS

- DMA

- Scanline based

- Region Update (MIPI DBI)

- Layer Overlay

- Number of layers

- Master Interface

- AMBA AHB 32bit

- AMBA AXI4 32 / 64bit

- Slave Interface

- AMBA AHB

- AMBA AXI4-Lite

Benefits

- Power Savings

- NEMA®|dc has two smart methods to reduce significantly the system power consumption:

- 1)TSCTMFB, Think Silicon Frame-buffer compression: A high quality lossy and 4bpp (bits-per-pixel) fixed rate scheme, which performs in real-time and requires minimal hardware. TSCFB yields into a reduction of frame-buffer size/traffic by 400-800%, depending on the color depth. The reduction of graphics memory size due to TSCTMFB enables systems using only internal on-chip memory by eliminating external DDR memory.

- 2)SSC, Smart Surface Composer: While composing on the-fly surfaces, NEMA®|dc lowers the system bandwidth by eliminating multiple memory read-write cycles and memory volume accesses, compared to a system where the GPU or CPU is entirely in charge of the composition process. SSC yields into a reduction of system bus/memory load by 40-60%, depending on the number and the format of the surfaces.

- TSTMFB and SSC combined are up to twenty (x20) times more power efficient than systems with a conventional display controller.

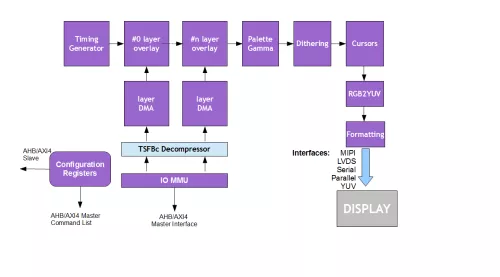

Block Diagram

Video

NEMA|dc accelerating Windowed Layers

This demo demonstrates the Nema|dc Multilayer Display Controller- Composition Engine. The demo runs on the Xilinx Zynq ZC706 development board driving a display with resolution of 1024x600 pixels . It features a single colored background, four framebuffer layers and a mouse pointer. Each layer incorporates a scaler (up/down with bilinear filtering) and a programmable blender. The CPU is responsible only for grabbing the mouse events and calculating the layers' position. All animations, rotating/blending/scaling/filtering operations and scene composition are done entirely by the NEMA|dc IP module without any CPU or GPU utilization

Applications

- NEMA®|dc is designed as a flexible back-end of the graphics-video path which works perfect in SoCs with GPU or in tandem with the host CPU in GPU-less systems.

- The possibility to choose from three different versions of NEMA®|dc makes it a perfect candidate to match the budget and suits applications spanning from ultra HD smart TVs (NEMA®|dc-700), to high-mid-range smartphones (NEMA®|dc-400) down to battery-limited embedded systems with simpler graphics requirements (NEMA®|dc-100).

- The Android Hardware Composer (HWC) driver allows NEMA®|dc-700 and NEMA®|dc-400 to act as a surface composer to accelerate graphics requests from the Skia-graphics library, Open Graphics APIs, or any graphics generating application running under the Android system.

Deliverables

- Deliverables include: complete set of synthesis, STA (Static Timing Analysis) scripts, OS drivers for Linux, Android, FreeRTOS, portable bare drivers and Android HWC driver.

- Documentation includes: IP manual, integration manual, software-library manual, application notes, demonstration platform, "How To Manual" with bare library application notes including programming descriptions and composition feature enablement.

- A reference design systems and demo-sets are available for platforms: Xilinx Zynq, Altera SoCkit.

- NEMA®|dc documentation includes the IP Manual, Integration Manual, Software Library Manual including example codes, and Application Notes.

Technical Specifications

Foundry, Node

synthesizable RTL

Maturity

silicon proven

Availability

Now - NOTE: NEMA DC only be licensed with NEMA GPU IP

Related IPs

- Master and Slave SPI Bus Controller

- Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- AHB Octal SPI Controller with PSRAM and XIP Support

- Customizable Display Controller with composition support

- Neural engine IP - Tiny and Mighty