Soft errors occur when high-energy charged particles alter the stored charge in a memory cell in an electronic circuit. The phenomenon first became an issue in DRAM, requiring error detection and correction for large memory systems in high-reliability applications. As device geometries have continued to shrink, the probability of soft errors in SRAM is becoming significant for some systems. Designers are using a variety of approaches to minimize the effects of soft errors on system behavior.

SRAM-based FPGAs store logic configuration data in SRAM cells. As the number and density of SRAM cells in an FPGA increase, the probability that a soft error will alter the programmed logical behavior of the system increases.

The Soft Error Detection is a user-configurable IP core, which allows the configuration of the IP and generation of a netlist and simulation file for use in designs. Please note that generating a bitstream may be prevented or the bitstream may have time logic present unless a license for the IP is purchased.

Soft Error Detection

Overview

Key Features

- 100% detection of single-bit errors

- 100% detection of two-bit errors within 10 adjacent frames

- 100% detection of multiple-bit errors within a 17-bit span

- (1-2-17)*100% detection of random multiple-bit errors

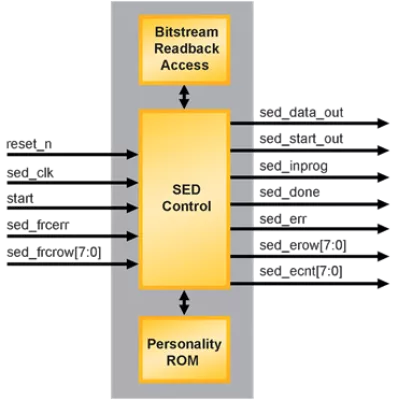

Block Diagram

Technical Specifications

Short description

Soft Error Detection

Vendor

Vendor Name

Related IPs

- Soft Error Mitigation (SEM) Core

- DO-254 Soft Error Mitigation

- CAN - Verifies communication, error detection, and data integrity in CAN systems

- APB Fundamental Peripheral IP, Serial Interface controller for multiple frame formats, SSP (by TI), SPI (by Motorola), Microwire (by NS), I2S (by Philips), AC - link (by Intel) and SPDIF (by Intel), Soft IP

- APB Fundamental Peripheral IP, I2C controller, Soft IP

- USB 1.1 Device Controller IP, Soft IP