SGPIO Initiator IIP

SGPIO Initiator is full-featured, easy-to-use, synthesizable design, compatible with SFF-8485 Specification for Serial GPIO (SGPI…

Overview

SGPIO Initiator is full-featured, easy-to-use, synthesizable design, compatible with SFF-8485 Specification for Serial GPIO (SGPIO) Bus revision 0.7. Through its SGPIO Initiator compatibility, it provides a simple interface to a wide range of low-cost devices. SGPIO Initiator IIP is proven in FPGA environment. The host interface of the SGPIO Initiator can be simple interface or can be AMBA APB, AMBA AHB, AMBA AHB-Lite,AMBA AXI,AMBA AXI-Lite, VCI, OCP, Avalon, PLB, Tilelink,Wishbone or Custom protocol.

SGPIO Initiator IIP is supported natively in Verilog and VHDL

Key features

- Compliant with SFF-8485 Specification for Serial GPIO (SGPIO) Bus revision 0.7

- Supports upto 256 hard disks

- Supports various operating frequency from 32Hz to 100KHz

- Supports to control High time and Low time of SGPIO Clock

- Supports transmit on rising edge and sample on falling edge

- Supports SGPIO LOAD to 0, when not exchanging a bit stream

- Supports SGPIO LOAD to 1, when SGPIO bus is not used

- Supports two blink generators A and B, used to control the output patterns

- Support two different modes

- Normal Mode

- General Purpose Mode

- Supports below different types of registers,

- Configuration registers

- Receive registers

- General purpose receive registers

- Transmit registers

- General purpose transmit registers

- Various kind of errors detection and interrupt handling

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

- Scan test ready

- Simple interface allows easy connection to Microprocessor/Microcontroller devices

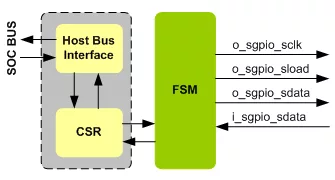

Block Diagram

Benefits

- Single Site license option is provided to companies designing in a single site.

- Multi Sites license option is provided to companies designing in multiple sites.

- Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

- Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

What’s Included?

- The SGPIO Initiator interface is available in Source and netlist products.

- The Source product is delivered in verilog.If needed, VHDL and SystemC can also be provided

- Easy to use Verilog Test Environment with Verilog Testcases

- Lint, CDC, Synthesis, Simulation Scripts with waiver files

- IP-XACT RDL generated address map

- Firmware code and linux driver package

- Documentation contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about GPIO IP core

A Generic Solution to GPIO verification

Ensuring reliability in Advanced IC design

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

ESD Protection for an High Voltage Tolerant Driver Circuit in 4nm FinFET Technology

From I2C to I3C: Evolution of Two-Wire Communication in Embedded Systems

Frequently asked questions about GPIO IP cores

What is SGPIO Initiator IIP?

SGPIO Initiator IIP is a GPIO IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this GPIO?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GPIO IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.