SATA 3 Host Controller on ZYNQ

Overview

The LDS SATA 3 HOST XZ7 IP incorporates the Transport layer, the Link layer and the PHY layer on a Xilinx Zynq speed grade 2 FPGA. The LDS SATA 3 HOST XZ7 IP is compliant with Serial ATA III specification and signaling rate is 1.5Gbps and scalable 6Gbs. The LDS SATA 3 HOST XZ7 IP is fully synchronous with system frequency (Clock_sys) at 37.5MHz in case of 1.5Gbps speed selection and 75MHz in case of 3Gbs speed selection and 150MHz in case of 6Gbs speed selection. The source code format is available for ease of customization. The customization can be done by Logic Design Solutions and DO254 documentation is available on request.

Key Features

- Physical Layer features

- Detect OOB and COMWAKE

- Detect the K28.5 comma character and provides a 32 bit parallel output

- Power management mode handled by state machine (shared between Phy and Link layer)

- Provides error indication to upper layers

- 8b/10b encoding and decoding in Xilinx Zynq GTX Macro

- Automatic Speed negotiation 6Gbs or 3Gbs

- Link Layer features

- Scrambling of tx data and descrambling of rx data

- CRC 32 calculation and check

- Report transmission status and error to Transport Layer

- Enable BIST loopback and pattern generation modes

- Auto inserted hold primitive to avoid FIFO overflow and underflow

- Partial and slumber power management modes

- CONT primitive management in receive and transmit

- The interface between the link layer and the transport layer is 32-bit wide

- Transport Layer features

- 48-bits sector address

- Programmed IO (PIO) and DMA modes

- Support BIST FIS transmission and reception

- Automatic error FIS retry capability

- Implement Shadow Registers and SATA SuperSet registers

- Simple synchronous CPU and DMA Interface for data transfers including DMA hold-off capability

- DMA interface can be connected easily to memory space or FIFOs (FIFO interface provided)

- Support DMA Abort primitive

- NCQ Support.

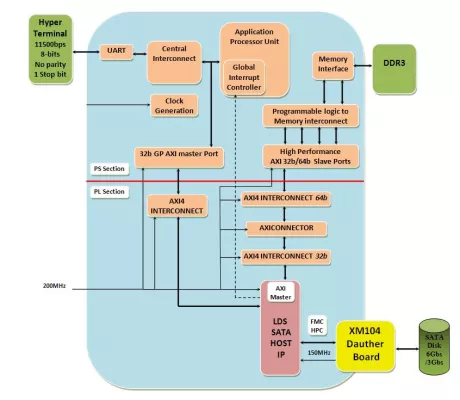

Block Diagram

Deliverables

- PlanAhead - EDK Project on ZC706 evaluation Board

- Netlist

- Source

- C source code

- Linux Driver under design

Technical Specifications

Short description

SATA 3 Host Controller on ZYNQ

Vendor

Vendor Name

Maturity

Good

Availability

Now

Related IPs

- Host Library for HDCP 2.3 on HDMI/DP Embedded Security Modules (generation 3)

- SATA-II Host Controller Core

- SATA-III Host Controller

- SpaceWire link controller with SpaceWire RMAP support and AMBA host interface

- 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface

- USB 2.0 Host Controller