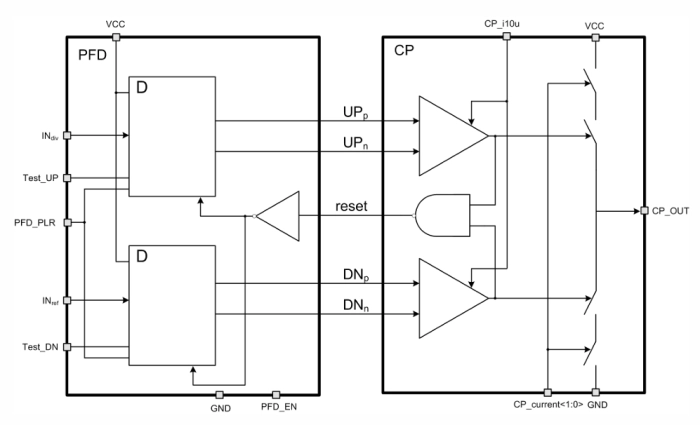

Phase-frequency detector (PFD) forms control signal for VCO tuning. PFD compares phases of divided VCO signal and divided reference oscillator signal and detects phase difference. Charge pump generates pulses for loop filter. Reference frequency 0.32…10 MHz. Output current is 40...140.5 uA.

The block is fabricated on iHP SiGe BiCMOS 0.25 um (SGB25V) technology.

PLL CMOS phase-frequency detector with ECL charge pump

Overview

Key Features

- iHP SGB25V

- Input signals with low amplitude

- Low disbalance of output current

- Portable to other technologies (upon request)

Block Diagram

Applications

- Phase-locked loop synthesizer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

PLL CMOS phase-frequency detector with ECL charge pump

Vendor

Vendor Name

Foundry, Node

iHP SiGe BiCMOS 0.25 um

Maturity

Pre-silicon verification

Availability

Now

Related IPs

- PLL ECL phase-frequency detector with ECL charge pump

- PLL ECL phase-frequency detector with ECL charge pump

- PLL CMOS phase-frequency detector with CMOS charge pump

- 0.1 to 25 MHz Phase-frequency detector with charge pump

- 24.84 MHz Phase-frequency detector with charge pump (input amplitude 150…210 mV)

- 1 to 20 MHz Phase-frequency detector and charge pump