The Low Latency interface (LLI) is a point-to point-interconnect that allows two devices on the separate chips to communicate as if a device attached to or present on the remote chip is resident on the local chip. The connectivity to the remote chip’s devices is through standard interconnects (AHB/AXI/OCP), using memory mapped transactions.

LLI is expressed as a layered transaction level protocol, where the Initiator and Target devices on two linked chips exchange transactions without software intervention. LLI supports two types of traffic classes, Low Latency and Best Effort. LLI primarily targets low-latency cache refill transactions using the Low Latency (LL) traffic class, and uses the Best Effort (BE) traffic class for accessing all other memory mapped remote devices. LLI also provides a special set of high priority transactions for transmitting sideband signals, like interrupts, between two chips connected with LLI link.

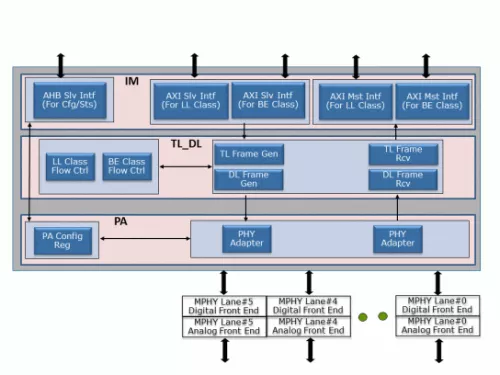

Arasan’s LLI Controller resides on each instance of a chip pair, and the two controllers communicate at a physical level through the M-PHY and their associated differential signals. The LLI Controller IP requires Arasan’s LLI specific MIPI M-PHY Type I IP as the Physical Layer and supports 1, 2, 3, 4 or 6 Lanes. The LLI Controller/M-PHY pairs on each chip together form a Low Latency Interface (LLI) bridge between the system buses/interconnects of two companion chips. This core is designed to be configurable as either a system bus master or slave, or both, for the Low Latency (LL) and Best Effort (BE) traffic classes defined in the MIPI LLI specification.

MIPI LLI Controller - (Low Latency Interface)

Overview

Key Features

- Compliant with MIPI LLI Rev 1.0 and M-PHY Type 1 Rev 2.0

- Delivered in Reuse Methodology Manual (RMM) compliant Verilog RTL format

- Small footprint

- Interfaces to on-chip interconnect infrastructure, like AHB or AXI or OCP buses

- Configurable to provide any or all of the following interfaces for the named traffic classes

- Slave Interface for Low Latency Traffic class

- Slave Interface for Best Effort Traffic class

- Master Interface for Low Latency Traffic class

- Master Interface for Best Effort Traffic class

- Provides AHB/AXI/OCP Slave Interface for PHY Adapter Layer management

- Uses Arasan’s LLI specific MPHY TYPE-1 as the physical layer with following characteristics

- HS Gears 1 and 2 support

- PWM Gear 0-7 support

- Digital interface from each MPHY is configurable to be 8-bits (Gears 1or 2) or 16-bits (Gear2 only)

- Configurable number of lanes available for all gears: 1, 2, 3, 4, or 6

- Automatically adapts to MPHY operational speed (HS Gear 1.. 2 or PWM Gear 0.. 7)

- Implements Transport/Data Link Layers of the LLI Specification

- Implements PHY Adapter Layer based on the number of configured M-PHY lanes

- Minimal latency across all the LLI layers

- Transaction, Data Link and PHY Adapter layers operates on a high frequency symbol clock

- Single point of Synchronization between Interconnect Adaptation and Transaction layers

- Optional Slave Only LLI for reduced gate count

- Supports test features as specified in the LLI specification

Benefits

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

Block Diagram

Deliverables

- Verilog HDL of the IP Core

- Synthesis scripts

- Verification environment

- User guides for design and verification

Technical Specifications

Availability

Now

Related IPs

- PSI5 IP Core Controller for Peripheral Sensor Interface 5 Communication

- MIPI CSI-2 Controller Core

- MIPI DSI-2 Controller Core

- High speed low latency AES-GCM pipeline, 100Gbps

- I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU

- MIPI I3C Controller Host/Target IP