The I3C bus (incl. PHY) is used for various sensors in the mobile/automotive system where the Host transfers data and control between itself and various sensor devices. The I3C interface is intended to improve upon the features of the I2C interface, preserving backward compatibility. This I3C defines a standard multi-Drop interface between Host processors and peripheral Devices (e.g., sensors). Implementing the I3C Specification greatly increases the flexibility system designers have to supplant incumbent interfaces (i.e., I2C, SPI, UART) and support a wide array of Devices of increasing complexity and diversity in their system (e.g., sensor subsystem) and at as low a cost as possible.

MIPI I3C PHY - TSMC (12nm, 7nm, 5nm, and 22nm) - GF 12nm

Overview

Key Features

- Two wire serial interface up to 12.5 MHz using Push-Pull

- Legacy I2C Device co-existence on the same Bus (with some limitations)

- Dynamic Addressing while supporting Static Addressing for Legacy I2C Devices

- Legacy I2C messaging

- I2C-like Single Data Rate messaging (SDR)

- Optional High Data Rate messaging Modes (HDR)

- Multi-Drop capability

- Multi-Master capability

- In-Band Interrupt support

- Hot-Join support

- Synchronous Timing Support and Asynchronous Time Stamping

Benefits

- Available in various foundry processes

- No external (off-chip) components required

- Can be ported to other processes.

- Silicon proven

- Extensive Quality Methodology

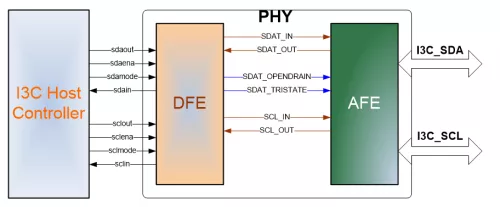

Block Diagram

Deliverables

- GDSII

- CDL netlist for LVS

- LIB files

- LEF files

- Scan-inserted netlist with test guide

- Behavioral model with verification environment

- DRC and antenna reports

- Design integration guide

- User guide

Technical Specifications

Foundry, Node

TSMC & GF

Maturity

Silicon Proven

Availability

Now

Related IPs

- 5V I/O and ESD in TSMC 12nm FFC/FFC+

- 1.8V and 3.3V Radiation-Hardened GPIO with Optimized LDO in GF 12nm

- 1.8V/3.3V I/O Library with ODIO and 5V HPD in TSMC 12nm

- ONFI 4.1 NAND Flash Controller & PHY & IO Pads on 12nm

- USB 3.0 femtoPHY in TSMC (28nm, 22nm, 16nm, 12nm)

- DDR4/3 PHY in TSMC (12nm, 16nm, 7nm)