MIPI DSI-2 v2.0 TRANSMITTER FOR COMBO C/DPHY

Key Features

- Compliant with MIPI DSI-2 v2.0 backward compatible to all DSI standards, MIPI D-PHY v3.x, MIPI C-PHY v2.0/2.1

- Up to 3 Gsps per trio using C-PHY. 17Gbps in 3 Trios.

- Up to 2.5 Gbps per data lane of D-PHY (V2.0). 10Gbps in 4 Lanes

- Programmable 1, 2, 3 (C-PHY) or 4 (D-PHY) Data Lane Configuration.

- Forward and Reverse Communication

- Configurable Virtual Channel up to 4

- Operate in continuous and non-continuous clock modes.

- Command and Video Mode are supported.

- Burst and Non-Burst modes are supported.

- Pulse and Event modes supported

- Color Modes: 16, 18, 24 and 36 bpp

- Display Stream Compression (DSC) Supported

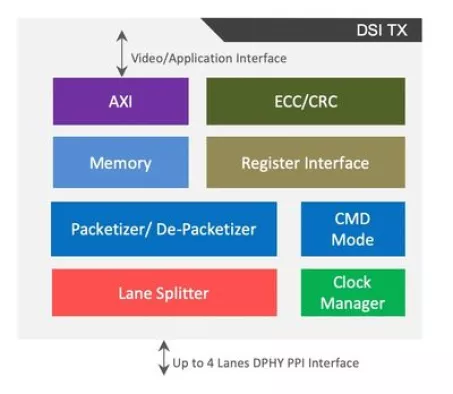

Block Diagram

Technical Specifications

Short description

MIPI DSI-2 v2.0 TRANSMITTER FOR COMBO C/DPHY

Vendor

Vendor Name

Maturity

Silicon proven, FPGA validated, Interop tested, Design verified

Availability

Immediately