The Arasan MIPI CSI-2 Transmitter IP Core functions as a MIPI Camera Serial Interface between a peripheral device (display module) and a host processor (baseband, application engine). The Arasan MIPI CSI-2 Transmitter IP provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

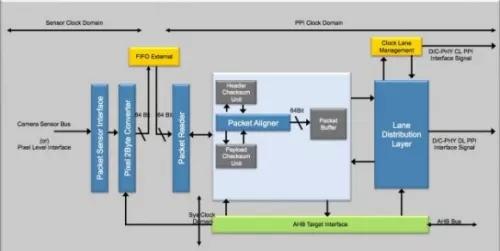

Pixel Data received from over the Camera Sensor Bus is packed into bytes by the Transmitter IP. The packing of the pixel into bytes follows the CSI-2 specification and based on the pixel format support. This IP calculates and appends an ECC/CRC value to a short packet (or) to the header of a long packet. Selection of ECC/CRC to the header is done based on the PHY connected. For the payload of a long packet carrying pixel data, this IP calculates its CRC value and appends to the packet as a Packet Footer (PF). The packet is buffered in a FIFO and sent to one or more D-PHY/C-PHY depending on the lane distribution scheme set by the camera sensor/user.

Arasan MIPI CSI-2 Transmitter is compliant to MIPI CSI-2 specification v2.1 and supports DPHY v2.1 and the MIPI C-PHY v1.2.

Arasan offers the C-PHY in a combination configuration that supports both C-PHY interfaces and D-PHY interfaces. Our implementation makes efficient use of the high frequency signally pins for a minimal overhead to support both physical interfaces.

MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

Overview

Key Features

- Use of either D-PHY/C-PHY by user configuration

- Lane is configurable depending on the bandwidth requirements of the application, up to 8-lanes for DPHY and up to 3-lanes for C-PHY

- Connectivity to DPHY/CPHY through MIPI PPI Interface

- High Speed (HS) transmit rates of 182Mbps to 6840Mbps (3Gsps) per lane with C-PHY interface

- High Speed (HS) receiver rates of 80Mbps to 1500Mbps per lane without calibration, 1500Mbps to 2500 Mbps with skew calibration and 2500Mbps to 4500Mbps with equalization in D-PHY interface

- Supports for Ultra Low Power Mode (ULPS)

- Supports for Alternate Low Power State (ALPS) in CPHY mode

- Support for Continuous and Non-Continuous Clock Mode

- Pixel formats supported

- RAW data type

- YUV data type

- RGB data type

- All user Defined data types / JPEG

- Generic 8-bit long packet data types

- Supports Data Type Interleaving

- Supports Virtual Channel Interleaving

- Pixel Level Input Interface for Image Sensor

- Supports Header and Payload Checksum

- Configurable for two mode of operation

- Store and Forward Mode – Stores the full pixel packet before forwarding.

- Cut through Mode – Initiates the HS transmission to D/CPHY as soon as the pixel information is received. Makes use of very shallow memory.

- Supports Multi Pixel Mode – Multiple Pixels per clock to bring down the sensor clock frequency to support higher resolution applications

- PPI Data Lane swapping as per user configuration

- Optional support for Compressed data formats

- Host interface for register configuration and monitoring,

- Used for programming both CSI-2 and PHY related registers. Reserved address space [0x00 – 0x0F] for the PHY related registers.

- Optional support for the AHB/APB Interface

Benefits

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

- Premier direct support from Arasan IP core designers

Block Diagram

Video

Arasan's MIPI CSI-2

A Webinar on the MIPI CSI-2

Deliverables

- Verilog HDL of the IP core

- User guide

- Synthesis scripts

- Lint report

- CDC report

- Verilog test suite

- Gate count estimation available upon request

Technical Specifications

Maturity

In Production

Availability

Now

Related IPs

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI CSI-2 with C-PHY Verification IP

- MIPI CSI-2 Tansmitter v 1.3, C-PHY compatible

- MIPI DSI Transmitter v1.2 Controller IP, Compatible with MIPI D-PHY & C-PHY

- MIPI C-PHY v1.2 D-PHY v2.1 RX 3 trios/4 Lanes - TSMC7FF 1.8V, North/South Poly Orientation

- Simulation VIP for MIPI D-PHY, C-PHY and A-PHY